# Linley Fall Processor Conference 2022

November 1-2, 2022

# **Session 3: Application-Specific Processors**

### Tailored Automotive Radar Processing with DSPs

David Bell, Product Marketing Manager for Tensilica CPU, DSP and AI Products, Cadence

### • 5G RAN Baseband Platform IP for Cellular Infrastructure Solutions

Eric Cowden, Sr Field Application Engineer, CEVA

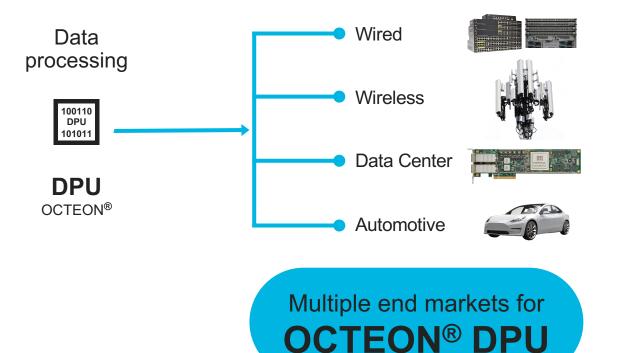

### DPUs: Where Will They Go Next?

Manoj Roge, Senior Director, Marvell Technology

Tailored Automotive Radar Processing with ConnX DSPs Linley Fall Processor Conference 2022

David Bell, Cadence, Product Marketing Director Nov 1, 2022

Agenda

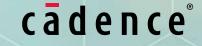

Sensors in Automotive

Radar Processing Requirements

**Tensilica ConnX DSP Introduction**

FMCW Radar Processing Performance with ConnX DSP

Summary

Source: Cadence

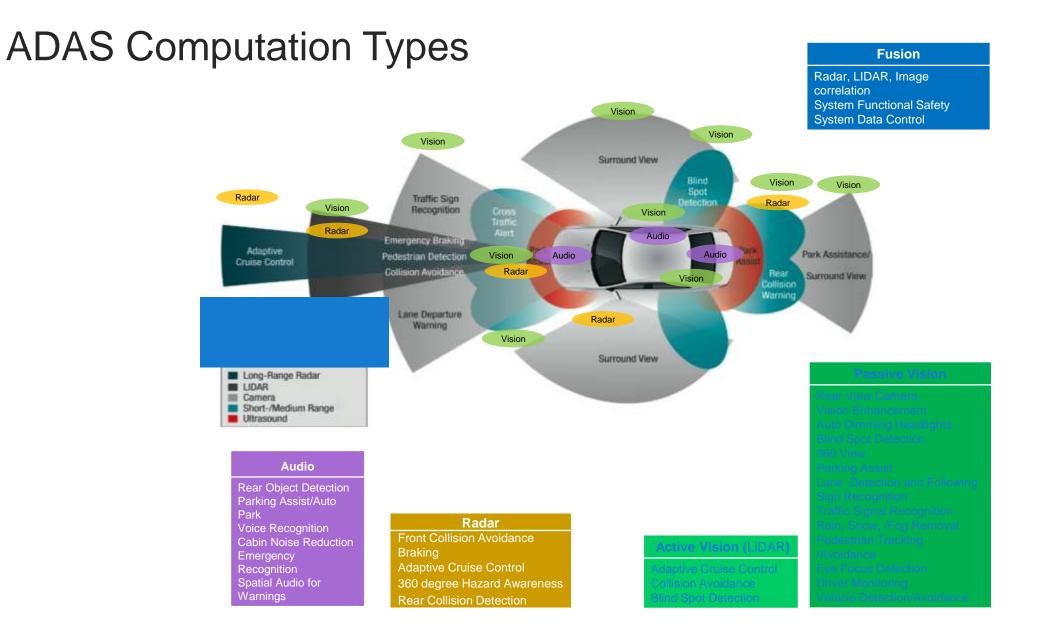

# **Comparative View of Sensors**

Sensor Fusion Key to Autonomous

No sensor type works well for all tasks and in all conditions, so sensor fusion will be necessary to provide redundancy for autonomous functions

WOODSIDE CAPITAL PARTNER!

Lidar

WCP

cadence®

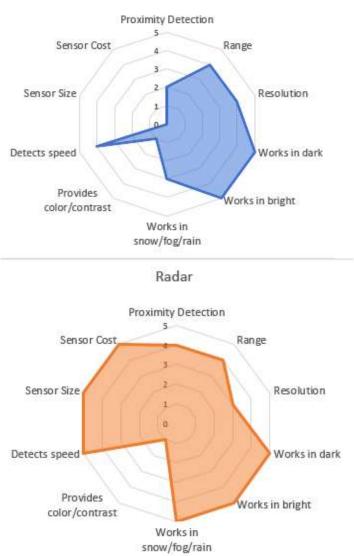

## **Automotive Sensors Market**

| Radars                | Uses                                                                                                                |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| Long Range            | ACC                                                                                                                 |

| Short/Medium<br>Range | Emergency Braking, Cross traffic alert, Blind<br>spot detection, Rear collision warning,<br>occupancy sensing, etc. |

| System                                                                  | Sensors                                                         |

|-------------------------------------------------------------------------|-----------------------------------------------------------------|

| Forward Collision Warning                                               | Radar, Camera, LiDAR                                            |

| Forward Collision Warning<br>and Mitigation/Active<br>Emergency Braking | Radar, Camera, LiDAR                                            |

| Adaptive Cruise Control                                                 | Radar, Camera                                                   |

| Traffic Jam Assist                                                      | Radar, Camera                                                   |

| Intelligent Speed Assist                                                | Camera                                                          |

| Blind Spot Detection                                                    | Radar, Camera                                                   |

| Lane Change Assist                                                      | Radar                                                           |

| Lane Departure Warning                                                  | Camera                                                          |

| Lane Keep Assist                                                        | Camera                                                          |

| Parking Assist                                                          | Ultrasonic Sensors                                              |

| Active Parking                                                          | Ultrasonic Sensors, Camera                                      |

| 360° View/Reversing Camera                                              | Camera                                                          |

| Cross Traffic Assist                                                    | Radar, Ultrasonic                                               |

| Pedestrian Detection                                                    | Camera, Radar, Infrared                                         |

| Cyclist Detection                                                       | Camera, Radar, Infrared                                         |

| Motorcyclist Detection                                                  | Camera, Radar, Infrared                                         |

| Animal Detection                                                        | Camera, Radar, Infrared                                         |

| Attention Assist                                                        | Camera, Steering Wheel, Other Vehicle Sensors, Biometric Sensor |

| Fatigue Detection                                                       | Camera, Steering Wheel, Other Vehicle Sensors, Biometric Sensor |

| Night Vision                                                            | Infrared                                                        |

| Adaptive Headlights                                                     | Camera, Steering Wheel                                          |

| High Beam Assist                                                        | Camera                                                          |

| Road Sign Recognition                                                   | Camera                                                          |

| Driver Monitoring Systems                                               | Camera                                                          |

|                                                                         |                                                                 |

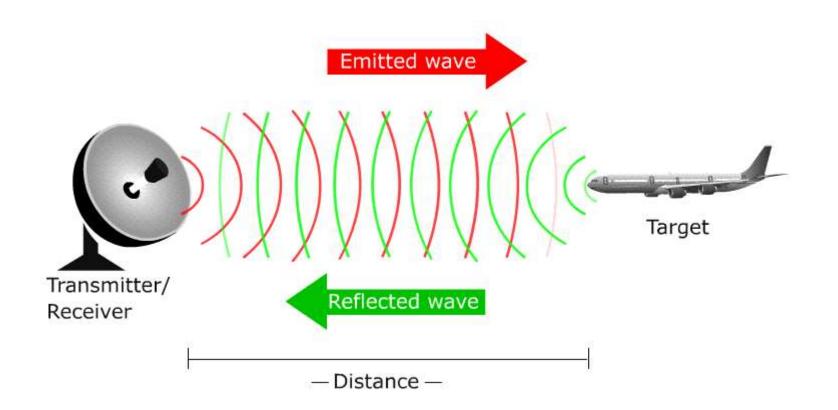

## Purpose of a Radar and Classification

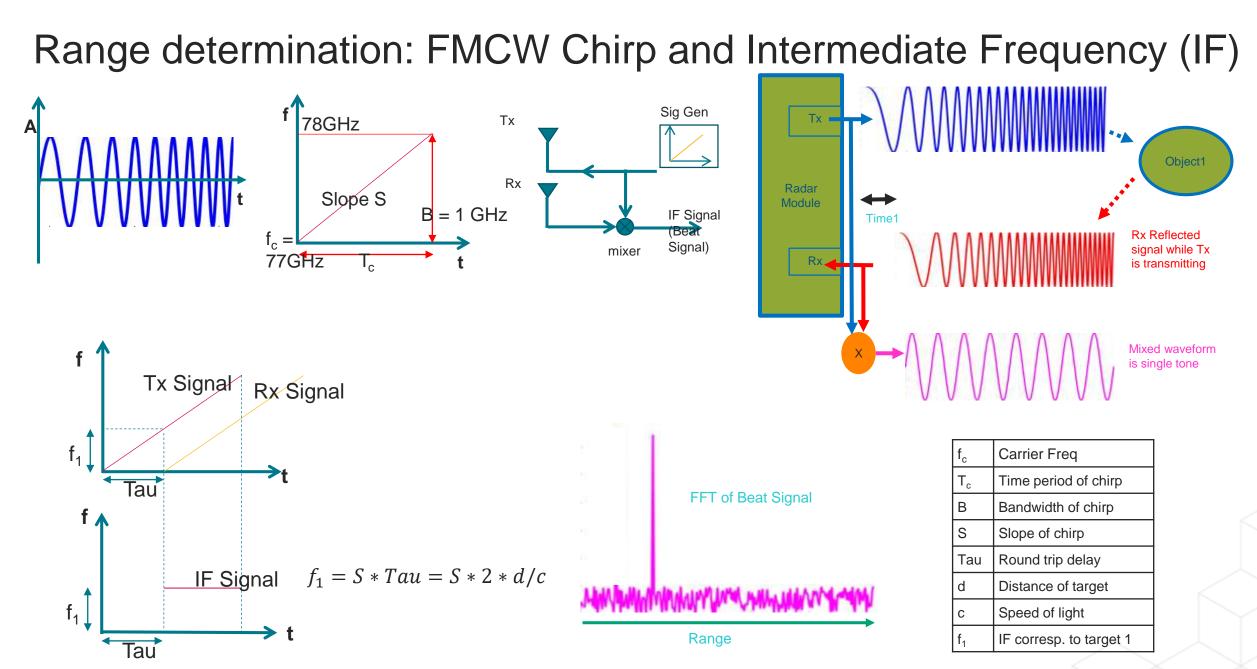

- Range determination: How far is the target?

- Velocity determination: How fast is the target moving relative to the radar?

- Angle determination: In which direction is the target moving?

- Some radars determine some of the above features

- Frequency Modulated Continuous Wave (FMCW) Radar can determine all three

- Maximum range determinable, maximum velocity determinable, maximum Field-of-View determinable

- Range resolution, velocity resolution and angle resolution

- Classification of automotive radar based on system properties as

Short-, Medium-, and Long-Range Radars

### **Basic Principle of a Radar**

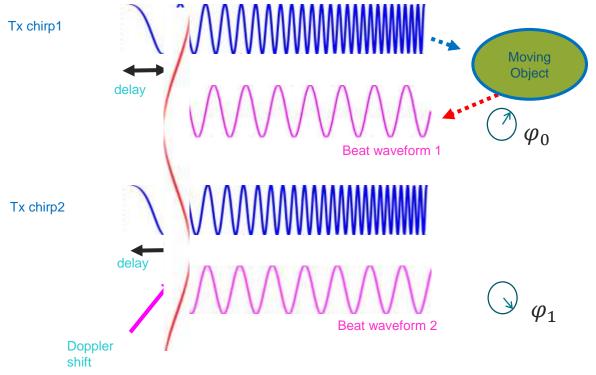

## Velocity Determination: How to Measure Velocity

- To measure the velocity of a target, transmit two chirps

- The change in phase of the IF signal across the chirps would correspond to the velocity (change in target location in a single chirp duration) of the target

- Phase difference between chirps  $\omega = 4\pi v T_c / \lambda$   $v = \lambda \omega / 4\pi T_c$

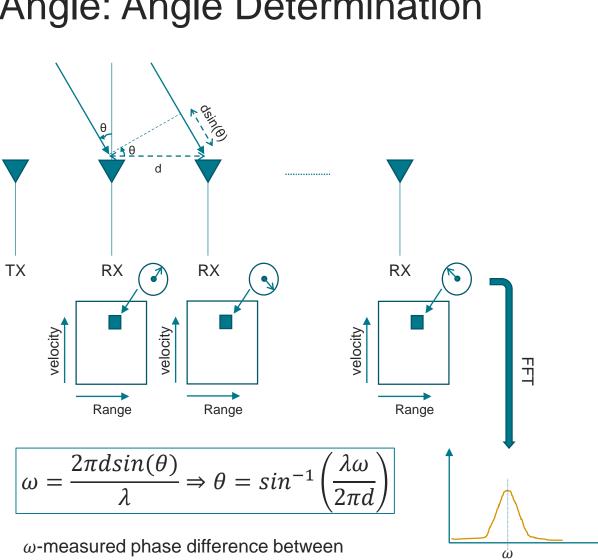

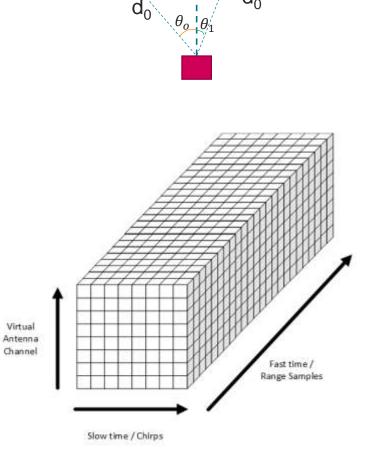

# Angle: Angle Determination

$V_0$

$d_0$

$V_0$

### Radar data cube

two antennas

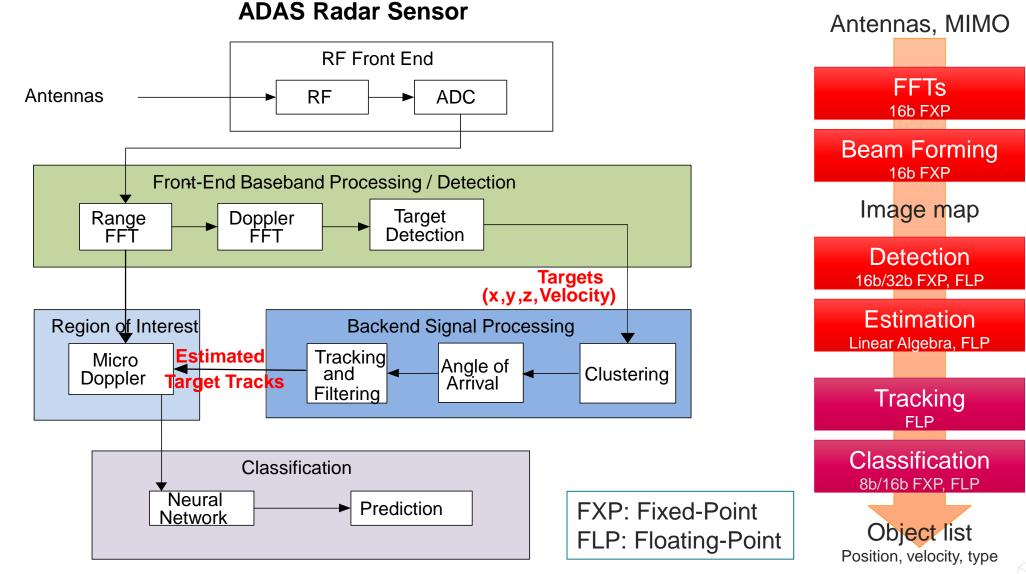

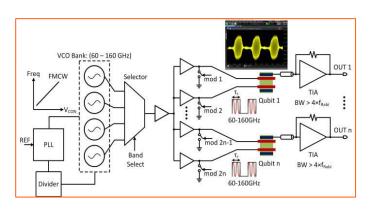

# FMCW Radar Signal Processing Chain

### cadence

## Tensilica ConnX DSPs

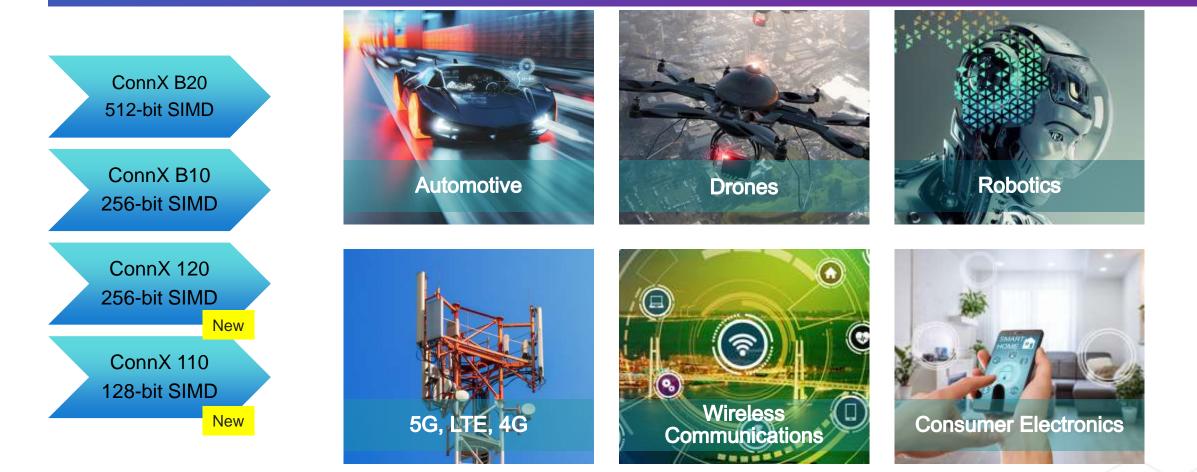

# Automotive, Consumer, Industrial

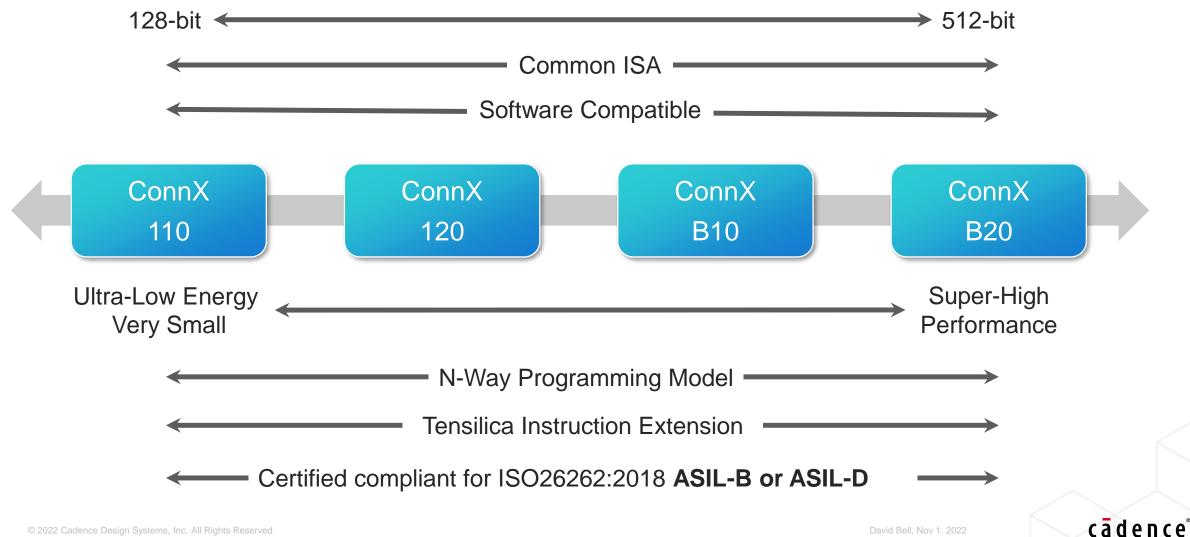

# Tensilica ConnX DSP Family

Scalable, configurable, extensible, flexible

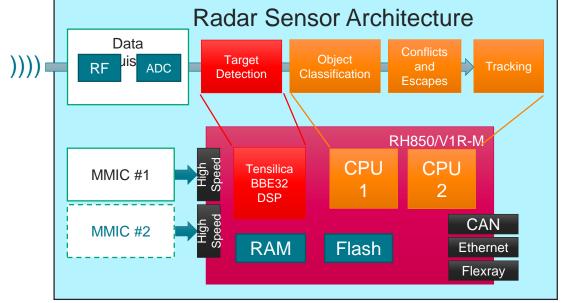

# Radar – Customer Success

- Renesas RH850/V1R-M

- Cadence<sup>®</sup> Tensilica<sup>®</sup> ConnX BBE32 DSP

- ISO26262: Functional Safety

- References

- <u>Renesas: Balancing performance, low-power and functional safety in</u> <u>ADAS Applications</u> (7/8/2016)

- <u>Renesas Radar Solution RH850/V1R-M (12/23/16)</u>

- NXP

- ConnX BBE32EP DSP-based solution with custom instructions (TIE)

- "...Specifically in radar, the contribution of Cadence has been fundamental. The [enhanced] DSP capability [allowed] us to develop algorithms that see with more accuracy, farther and to avoid ghosts or false positives..."

Source: https://youtu.be/LEwUfTs82II

#### 14 © 2022 Cadence Design Systems, Inc. All Rights Reserved.

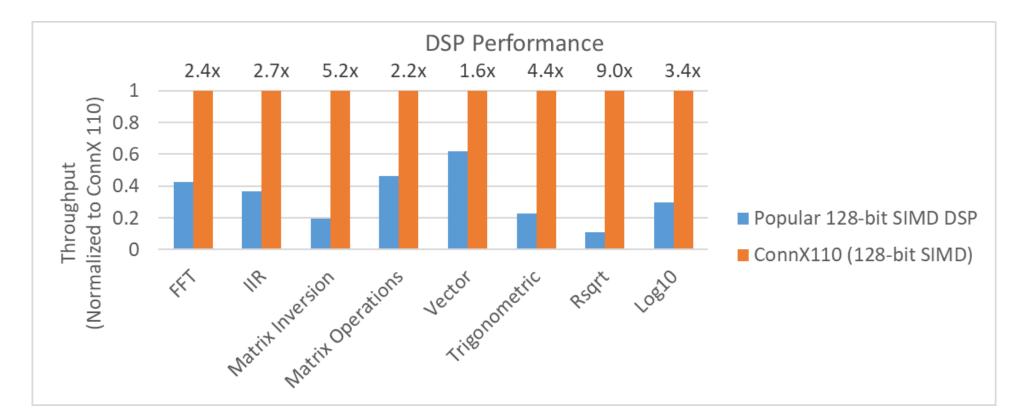

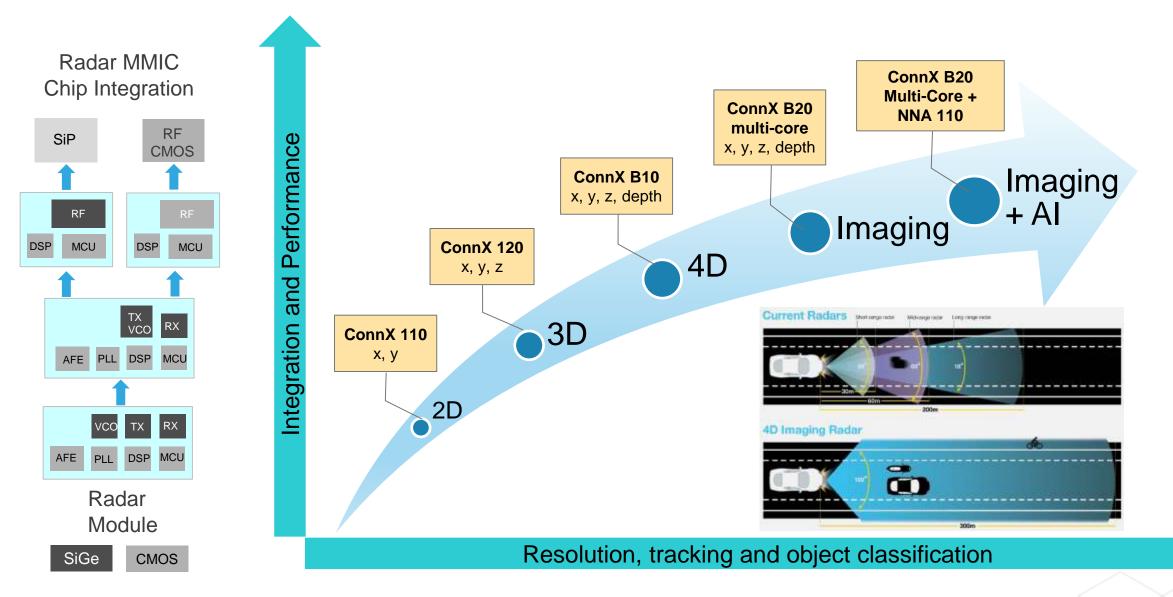

# **ConnX High-Performance DSPs**

- ConnX DSP provides high-performance processing across DSP and Math functions essential to radar processing

- ConnX 120 and B10 is ~2X the performance of ConnX 110

- ConnX B20 is ~4X the performance of ConnX 110

# **Radar Trend Implications**

- Detection requirements are increasing

- Number of objects, relative speeds, max distances and speeds, resolution

- System/algorithm requirements/constraints are increasing

- Number of channels/sensors, SIMO or MIMO

- Performance, precision, convergence, flexibility

- Memory hierarchy and accessibility

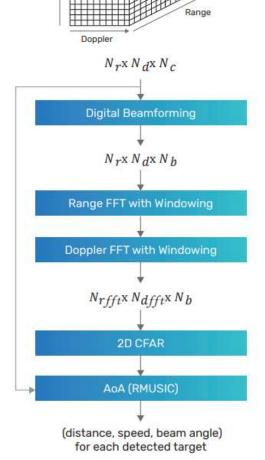

| Module                                  | Type of computation and trend requirements                                                                           |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| DBF                                     | Dot products                                                                                                         |

| Beam forming                            | > Faster with wider SIMD                                                                                             |

| RFFT, DFFT                              | FFT                                                                                                                  |

| Range-Doppler processing                | > Higher-precision complex FFT                                                                                       |

| Constant False Alarm Rate (CFAR)        | Averaging, sorting                                                                                                   |

| Detection                               | > Fast Peak Searches, Scatter Gather, Complex support                                                                |

| Multiple Signal Classification (MUSIC)  | Matrix Eigen decomposition, polynomial root finding                                                                  |

| High-Res Direction estimation algorithm | > Good Floating Point Linear Algebra                                                                                 |

| Clustering<br>Tracking                  | Tracking: Kalman Filter (Matrix multiplies/inversion)<br>Clustering: DBSCAN<br>> Good Linear Algebra, Scatter Gather |

# Software Libraries and Tools for ConnX DSPs

### Optimized DSP functions for radar applications

- Scalar/Vector fixed/floating-point, real/complex support

- Library source code available

| Library / Tool | Functions                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| NatureDSP      | Optimized Math functions for Logarithmic, Complex, FFT, FIR, IIR, Vector, Matrix operations                     |

| Eigen Library  | High-level library for linear algebra, matrix, vector, numerical solvers                                        |

| Radar Library  | Range FFT, Doppler FFT, Constant False Alarm Rate (CFAR), Extended Kalman Filter (EKF)                          |

| Matlab Toolkit | Simulink and Matlab code generation support to compile and simulate with ConnX DSP targets directly from Matlab |

https://www.cadence.com/content/dam/cadence-www/global/en\_US/documents/tools/ip/tensilica-ip/tensilica-dsp-code-generation-toolbox-with-matlab-simulink-wp.pdf

# FMCW SIMO Example Performance

ConnX B10/B20 - Fixed/Floating Point

| Description                                     | Mixed-Precision                                                          | Floating-Point Only            |

|-------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|

| Input Data Cube Size                            | 1024x                                                                    | 64x16                          |

| Digital Beamforming<br>(DBF)                    | Complex 16-bit fixed-<br>point samples<br>(represented in Q15<br>format) | Complex floating-point samples |

| Range-Doppler FFT (RFFT and DFFT)               | Complex 16-bit fixed-<br>point samples                                   | Complex floating-point samples |

| Constant False Alarm<br>Rate (CFAR)             | Real 32-bit fixed-point                                                  | Real floating-point samples    |

| Root Multiple Signal<br>Classification (RMUSIC) | 32-bit complex                                                           | x floating point               |

| Tensilica ConnX DSP                             | <b>Mixed-Precision</b>                                                   | Floating-Point Only            |

| ConnX B10                                       | 133MHz                                                                   | 259MHz                         |

| ConnX B20                                       | 84MHz                                                                    | 154MHz                         |

Channel

David Bell, Nov 1, 2022

# Summary: Choose Tensilica DSPs for Automotive Radar

| Fast development              | <ul> <li>Optimized software libraries for a wide variety of DSP functions in C</li> <li>Matlab Toolkit Integration</li> <li>Select from predefined hardware for algorithm acceleration</li> </ul> |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processing flexibility        | <ul> <li>Mixed Precision</li> <li>16- and 32-bit Fixed Point</li> <li>Half-, Single-, Double-Precision Floating Point</li> </ul>                                                                  |

| Scalability                   | <ul> <li>Code-compatible, scalable DSP software model</li> <li>Designed for multi-core implementations</li> </ul>                                                                                 |

| Differentiation               | <ul> <li>Only include the acceleration options needed for implementation</li> <li>Customize further with TIE if needed</li> </ul>                                                                 |

| Virtually unlimited bandwidth | <ul> <li>Add GPIO, FIFO, or SRAM interfaces up to 1024 bits each</li> <li>Create predictable connections to/from the rest of the SoC</li> </ul>                                                   |

| Functional safety             | <ul> <li>ISO26262 SEooC for ASIL-B and ASIL-D products</li> </ul>                                                                                                                                 |

# cadence®

For more information, please visit https://ip.cadence.com

© 2022 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks are the property of their respective owners.

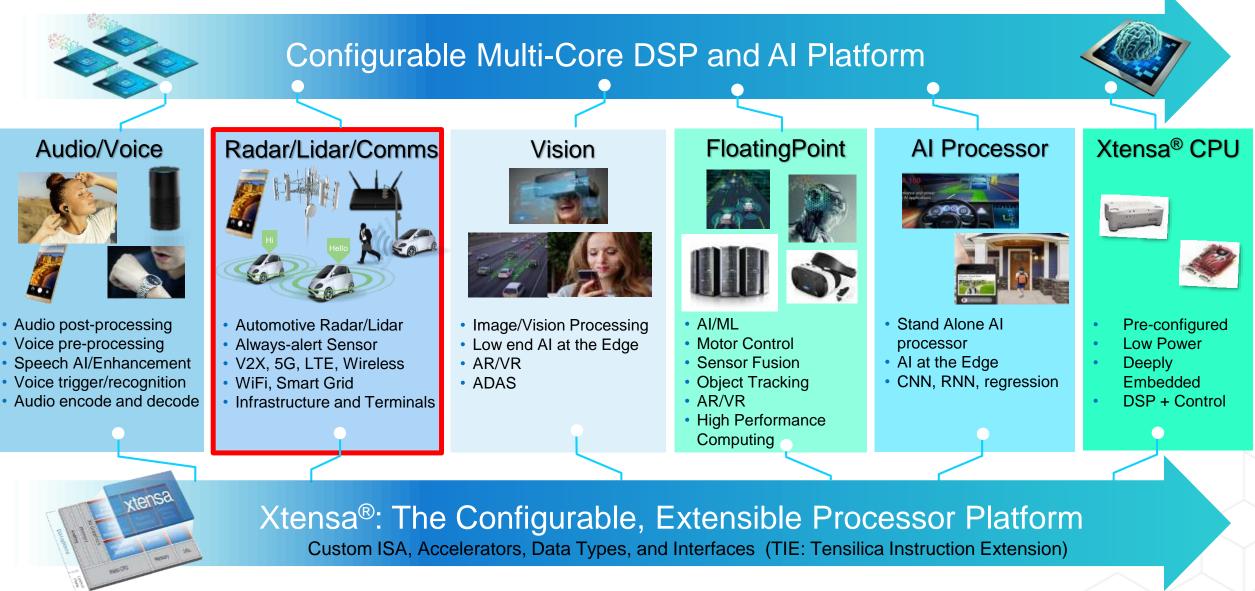

# **Tensilica Product Portfolio**

# ConnX DSPs

### **ConnX Advantages**

- Industry leading radar, lidar, and V2X DSPs

- Certified compliant for ISO26262:2018 ASIL-B or ASIL-D

- Optimized complex data processing (fixed and float)

- Linear algebra acceleration

- > Performance-enhanced FFT, FIR computation

- > Optimized for CFAR, beamforming, convolution processing

- Accelerations for communications (Viterbi, Turbo, LDPC)

- Optimized NatureDSP library, application SW examples

### **Main Functions**

- Radar sensing

- Lidar sensing

- > V2X

- Gesture sensing

- Sensor fusion

- Baseband PHY Layer

- Beamforming

# Eigen Library for ConnX DSPs

- High-level library for linear algebra, matrix, vector, and numerical solvers

- High-performance, reliable, and widely used to speed up math routines

- Explicit vectorization is performed for SIMD instruction sets

- Well-known API and industry standard

- $_{\circ}$   $\,$   $\,$  Used by CPU, GPU, and numerous platforms  $\,$

- The API is clean and expressive while feeling natural to C++ programmers

- Eigen library can be downloaded from <u>http://eigen.tuxfamily.org/</u>

AX = B $A^{-1}(AX) = A^{-1}B$  $(A^{-1}A)X = A^{-1}B$  $(I_n)X = A^{-1}B$  $X = A^{-1}B$

• Cadence provides the following components that can be overwritten over the downloaded open-source Eigen library

| Component                                              | Description                                                                                                                                                                                                    |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PacketMath.h and related header files                  | DSP architecture-specific header files for helping Eigen library to do better vectorization. It includes baseops and math functions. Details of currently supported data types showed in the table below.      |

| Eigen library CMake related files                      | The functionality and performance test files updated for Xtensa compiler and ISS                                                                                                                               |

| Eigen library support for full and half packet enabled | Eigen library provides a way to add support of half packet (half-SIMD) processing to improve performance of operations on non-SIMD multiple matrices. This half-packet support is added in <i>PacketMath</i> . |

### ConnX DSP PacketMath Support

|         | Single                | Double |

|---------|-----------------------|--------|

| real    | <ul> <li>✓</li> </ul> | ×      |

| complex | ✓                     | ×      |

Double-precision data types will be supported soon.

# NatureDSP Libraries for ConnX DSPs

### Rich and optimized DSP libraries for basic and advanced DSP functions

- Scalar/Vector fixed/floating-point, real/complex support

- Library source code available

Note: To cover the complete library routine list, all optional configurations have to be selected

| Category                              | Functions                                                                                                                                                                                                                                                                                               |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Math                                  | Scalar and vector for: arc cosine/sine/tangent, cosine/sine/tangent/cotangent, hyperbolic sine/cosine/tangent, sigmoid, logarithm, anti-<br>logarithm, exponential, square root, reciprocal, reciprocal square root, softmax                                                                            |

| Complex                               | Magnitude, phase, conjugate, exponent, combined cosine and sine, normalization, division, polar to cartesian and cartesian to polar conversion                                                                                                                                                          |

| FIR Filters                           | Convolution, auto/cross correlation, interpolation, decimation, polynomial fitting/interpolation                                                                                                                                                                                                        |

| IIR Filters                           | Biquad, lattice block IIR                                                                                                                                                                                                                                                                               |

| FFT                                   | Complex, real, FFT/IFFT, DFT, blockwise, and streaming                                                                                                                                                                                                                                                  |

| Vector Operations                     | Product, sum, magnitude, reciprocal, division, transcendental, peak search, mean                                                                                                                                                                                                                        |

| Matrix Operations                     | Multiply, Transpose, Hermitian Product, Streaming-Block order conversion, Interleaving/De-interleaving                                                                                                                                                                                                  |

| Matrix Decomposition<br>and Inversion | QR decomposition and Back substitution, Cholesky MMSE Solver, Cholesky Decomposition/Forward and Backward substitution, Direct Matrix Inversion, Matrix Inversion by Gauss-Jordan, LU Decomposition, Determinant, Linear equation solution, Singular Value Decomposition, Eigenvalues and Eigen vectors |

| Communications                        | CRC, de-spreading, modulation, slicer, convolutional encoding, bit manipulation, PRBS Generation, space time coding                                                                                                                                                                                     |

# Radar Libraries for ConnX DSPs

### **Optimized DSP functions for Radar Applications**

- Scalar/Vector fixed/floating-point, real/complex support

- Library source code available

Note: To cover the complete library routine list, all optional configurations have to be selected

| Category                            | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Range FFT                           | Range FFT(RFFT) is used to calculate range of the targets by computing forward Fast Fourier Transform(FFT) on real/complex input data with/without window. It calculates blockwise FFT on L blocks of N input samples, where supported values of N (FFT size) are the power of 2 ( $2^n$ n) where n = 4, 5, 12 and L>0.                                                                                                                                                                                                                                                    |

| Doppler FFT                         | This function computes the forward FFT on complex streaming order input data with/without windowing. It provides three types of outputs which are complex FFT spectrum, real normalized magnitudes of complex FFT spectrum, and Log (base 2) of normalized magnitudes of FFT spectrum.                                                                                                                                                                                                                                                                                     |

| CFAR                                | False Alarm Rate (CFAR) module is an adaptive thresholding technique that detects targets present in a Range Doppler Image (RDI). Each pixel of the RDI is called a cell, and whether the target is present in the cell or not is determined by CFAR algorithm. A specific cell for which this algorithm is applied is referred to as the Cell Under Test (CUT).                                                                                                                                                                                                           |

| Tracking: Extended<br>Kalman Filter | Kalman filter addresses the general problem of estimating the state of a discrete-time controlled process governed by a linear stochastic difference equation. If the process to be estimated and (or) the measurement relationship to the process is non-linear, we can linearize the estimation around the current estimate using the partial derivatives of the process and measurement functions to compute estimates. The Extended Kalman Filter (EKF) is the nonlinear version of the Kalman filter, which linearizes an estimate of the current mean and covariance |

# Cadence Tensilica Code Generation Toolbox

- Matlab toolbox-based package is provided for ConnX B10/B20 DSPs

- User guide describes the details of the installation procedure

- Package provides both Simulink and Matlab code generation support

- Generate code targeting the Cadence Tensilica ConnX DSPs

- Code Replacement for certain kernels from NatureDSP library is provided

- NatureDSP library is required to be built separately and provided during the setup

- Compile optimized code using the Cadence Xtensa C/C++ Compilers

- Run the compiled code using the Cadence Xtensa Instruction Set Simulator

- Check the results and behavior of code running in Processor-In-the-Loop (PIL) manner against the Matlab/Simulink's simulated test vectors.

- Windows and Linux environments are supported

- Current package works with Matlab R2021a

- Toolboxes required

- Embedded Coder

- Matlab Coder

- Simulink and Simulink Coder (Required for Simulink code generation)

# Industry Leading Radar / Lidar DSPs for Automotive Applications

### Autonomous Vehicle Design Win

- Global Tier 1 Semiconductor Vendor

- Autonomous Vehicle

- Multiple ConnX B20 DSPs

- 4D Imaging Radar

### Radar Design Wins Globally

- NA, EMEA, APAC

- Global Tier 1 Semiconductor Vendors

- RTL Delivered

- Silicon in Mass Production

### Tensilica ConnX - Scalable Radar / Lidar Processing Solution

# CEVA

PentaG-RAN 5G RAN Baseband Platform IP for Cellular Infrastructure Solutions

Application-Specific Processors November 1, 2022

Eric Cowden FAE

www.ceva-dsp.com

© November 2022 CEVA, Inc.

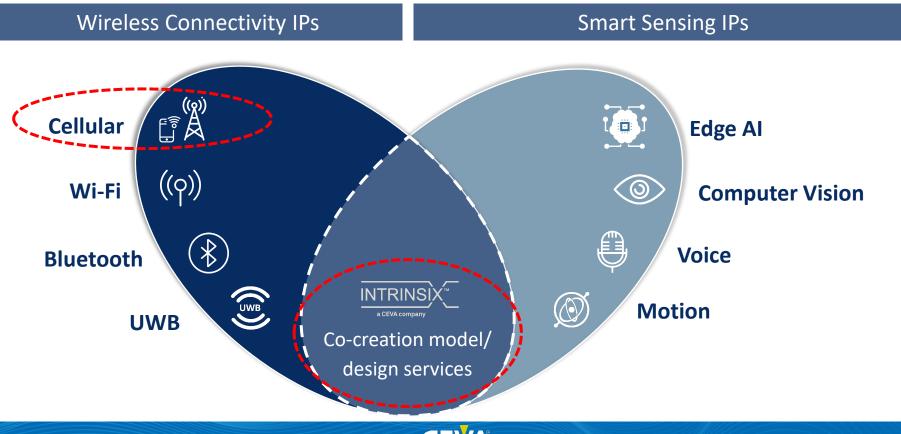

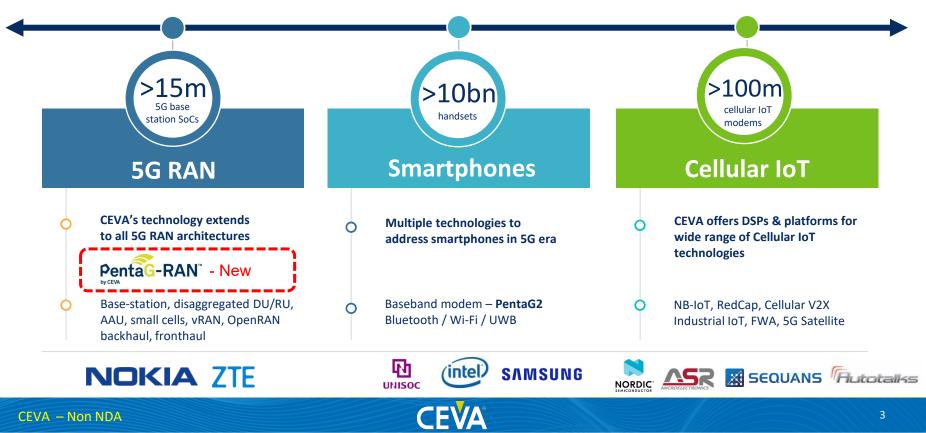

### **Technology Portfolio – Enabling Smart Edge Devices**

### Building on CEVA's Legacy as Leading Cellular IP Vendor

### From Infrastructure to IoT

# **5G RAN Technology Trends**

5G networks are evolving in several vectors, all pointing towards network openness and sophistication:

### Massive MIMO and Beamforming (BF)

- Radio Unit (RRU) is becoming a Massive MIMO 32/64/128 antenna Active Antenna Unit (AAU) with massive compute requirements

- Significant complexity in beamforming computation and management need for baseband processing in RRU in antenna site

### **Open RAN (O-RAN)**

- O-RAN specifying common and open interfaces between RAN components

- Emergence of new OEMs need for new merchant silicon with efficient baseband processing to replace power and cost inefficient FPGAs and COTS platforms

### Virtualized RAN (V-RAN)

- VRAN Running virtual SW defined networks on COTS platforms

- Aggregation of multiple links on single platform Massive compute requirements for Baseband Unit

### **Proliferation of Small Cells**

- For indoor, dense deployments, and mmWave

- Large volume and easier penetration new players

#### CEVA – Non NDA

## **5G RAN Massive MIMO Technology Challenge**

- Immense compute needs for massive 64x64 antenna arrays. Existing COTS solutions are not efficient and cannot scale to massive MIMO dimensions

- Diverse workloads in 5G physical layer require complex and heterogeneous L1 sub-systems, and optimal HW/SW partitioning

- New Entrants to the market are intimidated by the challenges posed to develop ASICs for this huge market opportunity

- There is a design gap within the semiconductor industry for 5G baseband processing, where there is a scarcity of design and architecture expertise, particularly within the PHY and radio domains, which are highly complex in nature

### The Need for Cost Effective ASIC Solutions

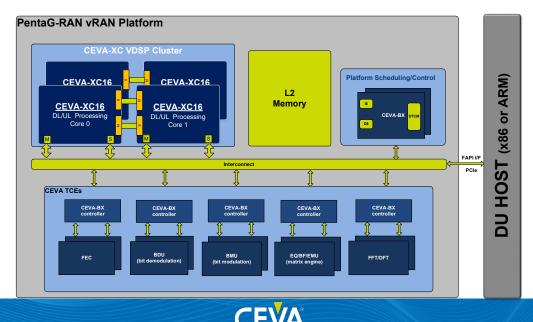

#### Industry's First 5G Baseband Platform IP for Open RAN ASICs

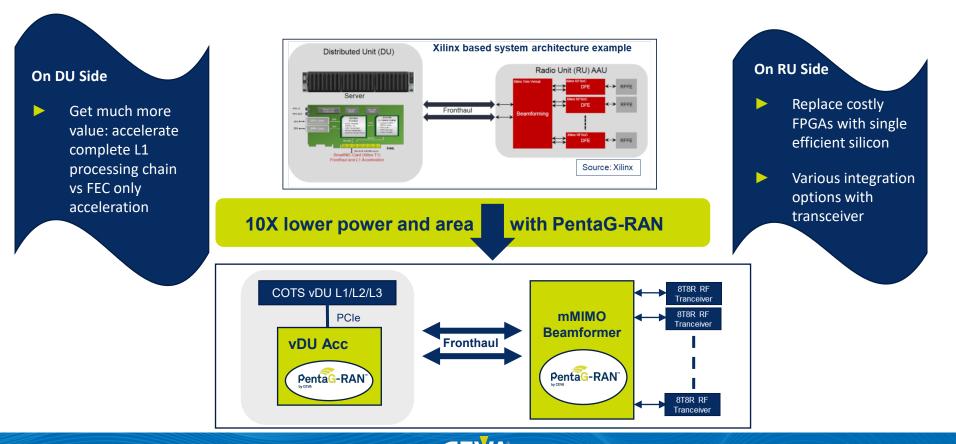

- PentaG-RAN is targeting cellular infrastructure ASICs in base station and radio configurations, from small cell to Massive MIMO

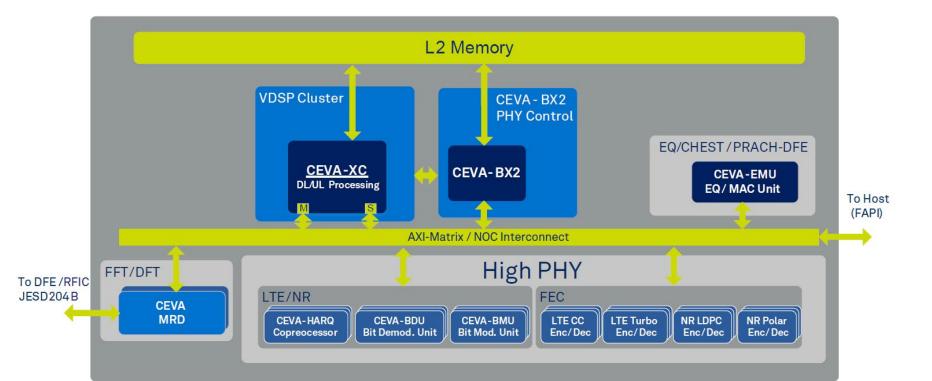

- PentaG-RAN is a heterogeneous baseband compute platform that provides a complete licensable L1 PHY solution with optimal hardware/software partitioning, integrating best in class vector DSPs and complete acceleration of signal datapath using efficient hardware accelerators

- PentaG-RAN platform delivers up to 10X savings in power and area compared to available FPGA and COTS CPU based alternatives

- PentaG-RAN is also offered in SoC co-creation design model using CEVA-Intrinsix

# **PentaG-RAN** Configuration for Small Cell and DU

#### CEVA - Non NDA

Ę

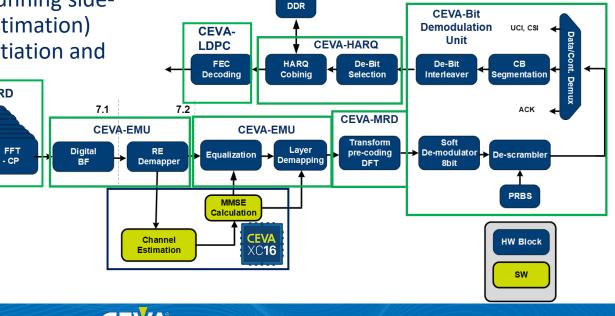

### **Optimal HW/SW Partitioning**

- Complete acceleration of signal path processing. Wide range of acceleration blocks

- Flexible SDR platform for running sidealgorithms (e.g. channel estimation) allowing customer differentiation and secret sauce

#### 5G UL Processing Chain Data Path Acceleration

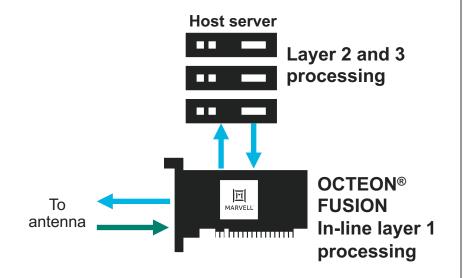

### **Massive vRAN DU Acceleration**

- PentaG-RAN can be used as vRAN inline acceleration compute resource to COTS platforms (x86 or ARM based)

- Based on market leading CEVA-XC

- Baseband platform also includes:

- CEVA-BX2 scalar controller/DSPs for PHY control and sequencing

- **Comprehensive** set of HW accelerators and co-processors for accelerating **complete** data path

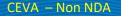

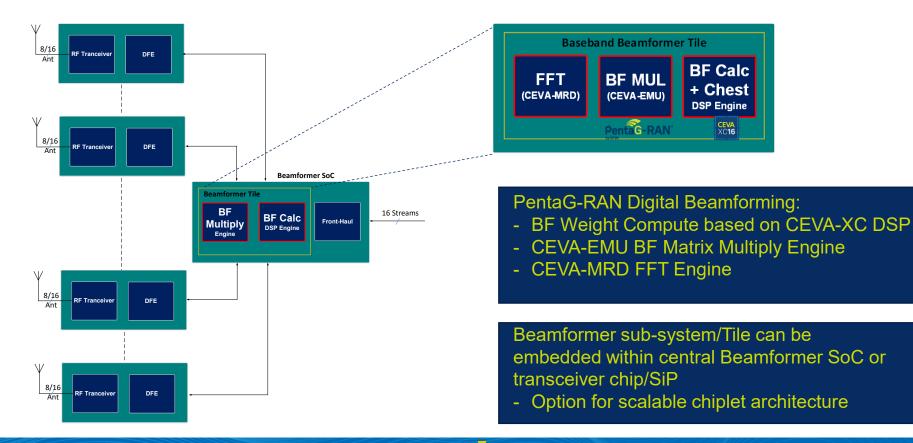

# **PentaG-RAN** Configuration for RRU and Massive MIMO

### **Typical Open RAN Radio Unit**

### **Massive MIMO Beamformer SOC**

#### **PentaG-RAN Massive MIMO Radio Platform**

Heterogeneous scalable IP platform comprised from DSP cores (best in class XC16 and BX2) and HW FFT/DFT mMIMO L2 Memory accelerators (co-processors) Beamformer Precoding CEVA-MRD **RU DSP Module** Optimal HW/SW partitioning allowing solution scaling and meeting competitive power CEVA-XC CEVA-MRD Baseband VDSP consumption targets DFE / RFIC JESD204B CEVA-EMU DSPs handle advanced algorithms CEVA-MRD **AXI Matrix Interconnect** FrontHaul like channel estimation, BF calculation, etc. CEVA-MRD PHY Control & **Co-Processing Cluster** Data path fully mapped to HW CEVA-EMU CEVA-BX2 acceleration PRACH DFE

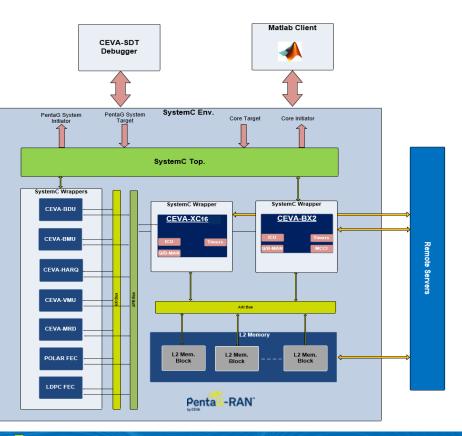

#### **Virtual Platform Simulator**

- An integrated System-C simulation environment that allows system engineers, architects and SW developers to model, profile and debug in pre-silicon

- Supporting CEVA's vector & scalar DSP cores and HW accelerators

- Fast prototyping and architecture definition

- Strong and effective IP evaluation and PoC tool

- Seamless MATLAB interface for algorithmic development and tests

- Available for evaluation and demos

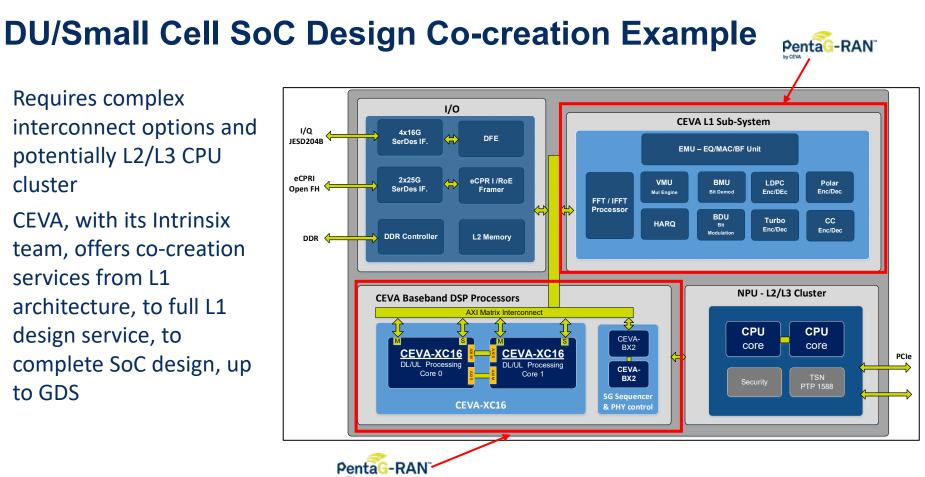

# Trusted Partnership: SoC Co-Creation

## **CEVA's 5G Co-Creation Offering**

- CEVA's PentaG-RAN is a unique 5G platform IP offering allowing customers to quickly introduce their own 5G SoCs

- CEVA can customize this comprehensive solution to fit Customer's needs

- Map customer use case to PentaG-RAN platform

- Complete architecture spec, solution dimensioning

- Interconnect definition (to transceiver, JESD, Fronthaul, eCPRI, etc.)

- Adaptation to specific process node and operating conditions

- SW architecture, and foundation SW framework

- Intrinsix team (SoC design services of CEVA) can supply complete modem design services, from architecture up to GDS

- These steps ensure Customer can identify its differentiation opportunity as well as offload development resources

# **Thank You**

#### www.ceva-dsp.com

© 2022 CEVA, Inc. and/or its subsidiaries. All rights reserved. All specifications are subject to change without notice.

CEVA – Non NDA

# DPUs: Where Will They Go Next?

Manoj Roge Sr Director, Processor Business Unit, Marvell Linley Fall Processor Conference, November 2022

#### Forward-looking statements

Except for statements of historical fact, this presentation contains forward-looking statements (within the meaning of the federal securities laws) including, but not limited to, statements related to market trends and to the company's business and operations, business opportunities, growth strategy and expectations, and financial targets and plans, that involve risks and uncertainties. Words such as "anticipates," "expects," "intends," "plans," "projects," "believes," "seeks," "estimates," "can," "may," "will," "would" and similar expressions identify such forward-looking statements. These statements are not guarantees of results and should not be considered as an indication of future activity or future performance. Actual events or results may differ materially from those described in this presentation due to a number of risks and uncertainties.

For factors that could cause Marvell's results to vary from expectations, please see the risk factors identified in Marvell's Quarterly Report on Form 10-Q for the fiscal quarter ended July 30, 2022, as filed with the SEC on August 26, 2022, and Marvell's Annual Report on Form 10-K for the fiscal year ended January 29, 2022, as filed with the SEC on March 10, 2022, and other factors detailed from time to time in Marvell's filings with the SEC. The forward-looking statements in this presentation speak only as of the date of this presentation and Marvell undertakes no obligation to revise or update publicly any forward-looking statements.

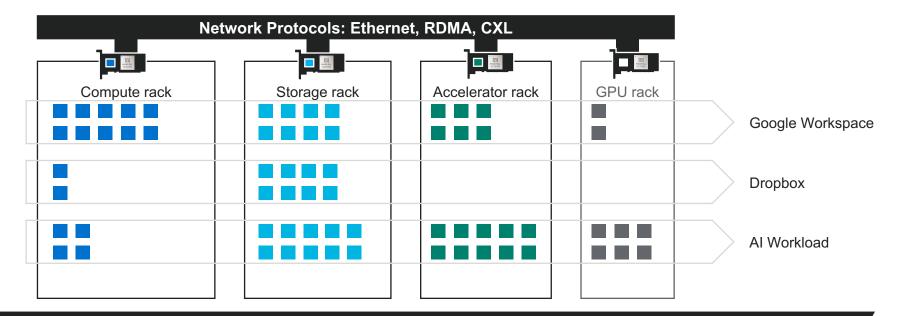

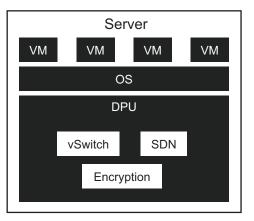

### DPU need driven by data centric applications

#### Future Data Centers: Composable, software-defined, hardware-accelerated

#### **DPUs manage composability, accelerate workloads**

### DPU in every server!

Our View of a Data Center Computer

Microsoft H2RC'16: "CPU is complexity offload engine for FPGA!"<sup>1</sup>

#### Amazon 2019 re:Invent – "All new instance launches use the Nitro System"<sup>2</sup>

#### rroming a warenouse-scare computer Svilen Kanev<sup>†</sup> Juan Pablo Darago<sup>†</sup> Kim Hazelwood<sup>†</sup> Harardu University Universidad de Buenes Aires Yahoo Labs Parhasarathy Ranganathan Tipp Moseley Gui-Yeon Wei Harard University Goode Goole Harardu University

#### Meta

"Microservices spend as few as 18% of CPU cycles executing core application logic"<sup>3</sup>

#### Google

"Data center Tax" can comprise nearly 30% of cycles<sup>4</sup>

1: H2RC 2016 keynote.

2: AWS reinvent 2019

3: Accelerometer paper

4: Profiling a warehouse-scale computer paper

#### 6

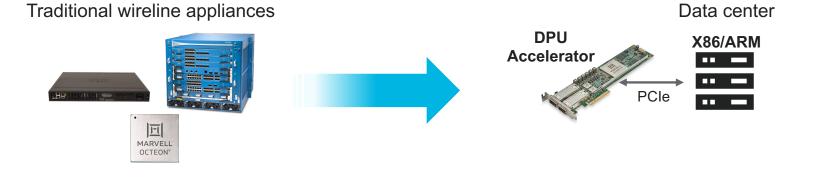

### Transition to virtualization

Traditional RAN/carrier Data center  $\mathfrak{X}$ O-RAN 9009 जि M MARVELL MARVELL OCTEON\* **OCTEON**° vRAN Fusion

### Applications require versatile mix of accelerators

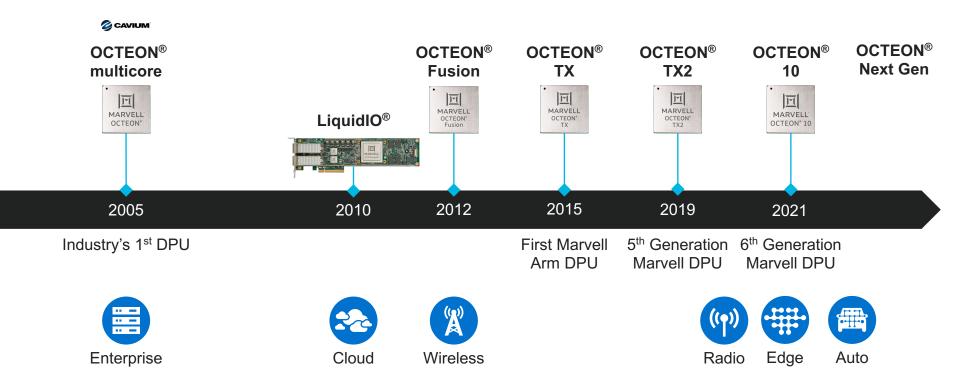

### OCTEON®: The original DPU platform

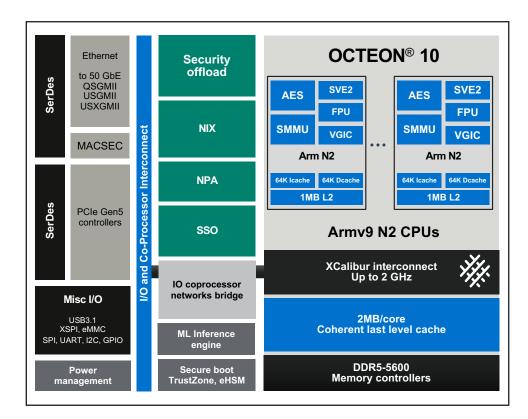

## OCTEON® 10 architectural overview

#### Scalable Compute

ARMv9.0 64-bit Neoverse N2 cores

#### Memory subsystem and connectivity

- IMB/core L2, 2MB shared last level cache

- DDR5 w/ sideband-ECC and memory encryption

- XCalibur mesh interconnect

#### Hardware acceleration

- Highly-virtualized, software-friendly NIC

- Packet processing, QoS, hierarchical queues with shaper and WDRR scheduler

- Inline and Co-processor security (SSL/IPSec)

- Compression, Decompression

- Inline ML inference engine

- Secure boot + embedded hardware security module

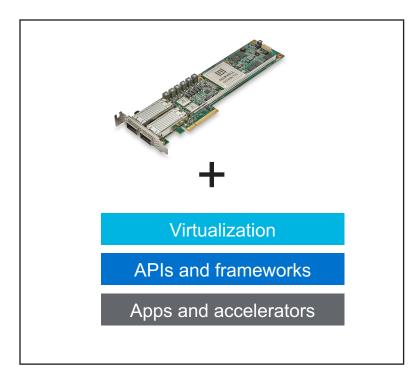

### Platform strategy

- DPU PCIe cards

- Robust and open source software support

- Partner ecosystem

#### Marvell PCIe accelerator cards

|              | CN98                     | CN106                               | CN103                    |  |

|--------------|--------------------------|-------------------------------------|--------------------------|--|

| Part Number  | WA-CN98-A1-PCIE-4P100-R1 | WA-CN106-A1-PCIE-2P100-R1           | WA-CN103-A0-PCIE-4P50-R1 |  |

| Port config  | 4x 100G PAM4             | 2x 100G PAM4                        | 4x 50G PAM4              |  |

| PCle         | Gen4                     | Gen5                                | Gen5                     |  |

| Core         | 36x ARM V8 TX2           | 24x ARM V9 N2                       | 8x ARM V9 N2             |  |

| Availability | Now                      | *                                   | 1Q CY23                  |  |

|              |                          | Announcing<br>General availability! |                          |  |

#### CN106 based PCIe card

| Part number                                      | WA-CN106-A1-PCIE-2P100-R1                            |  |  |  |

|--------------------------------------------------|------------------------------------------------------|--|--|--|

| Features                                         | Capability                                           |  |  |  |

| I/O                                              | 2 x 100G PAM4<br>PCIe Gen 5                          |  |  |  |

| Memory                                           | 6 x 40bit DDR5@ 5200MTs<br>w/ECC, 8-40GB total       |  |  |  |

| ARM cores                                        | 24 ARM N2, 2.5GHz,<br>100 SPECINT2017                |  |  |  |

| Performance                                      | 120 MPPS, 120Gbps                                    |  |  |  |

| IPSEC, RSA 2K,<br>1KB OpenSSL,<br>TLS1.3 support | 120Gbps IPSEC, 24Kops RSA<br>2K, 120Gbps 1KB OpenSSL |  |  |  |

| Hard ML block                                    | Yes, 16TOPS                                          |  |  |  |

| Availability  | Date     |

|---------------|----------|

| SDK11 support | Now      |

| Order in qty  | Nov 2022 |

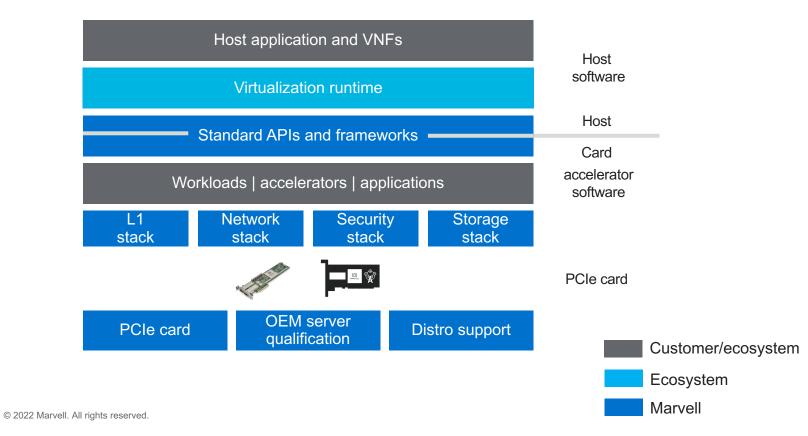

#### **DPU** solutions

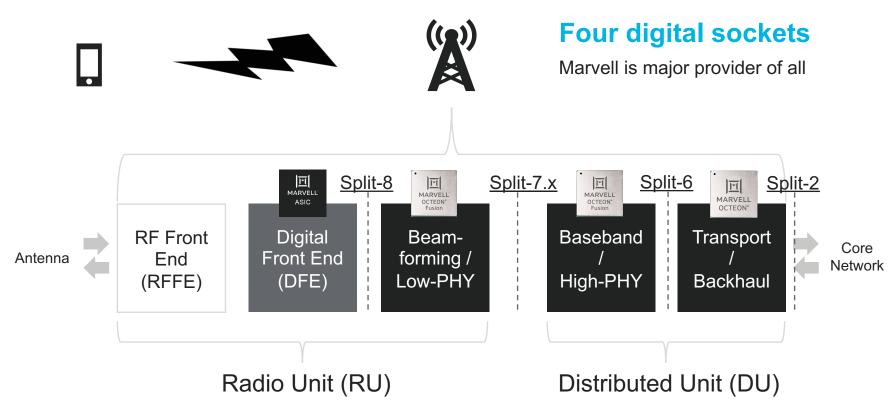

### Industry-leading 5G infrastructure portfolio

### 5G O-RAN solution: open, scalable, best-in-class

The combination of Nokia's ReefShark advanced System on Chip (SoC) technology, developed in cooperation with Marvell, with standard Commercial-Off-the-Shelf (COTS) servers will enable the Open RAN system to reach functionality and performance parity with traditional mobile radio networks. Nokia's ReefShark SoC boosts the Layer-1 processing capability, which is necessary to connect many users to the mobile base station and support high levels of mobile data traffic.

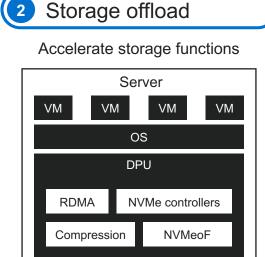

#### Data Center use cases

Network offload

#### Accelerate networking functions

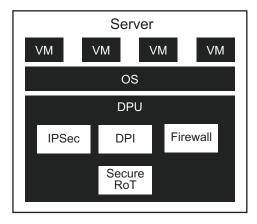

Security offload

3

#### Isolate tenants from host

#### DPU delivers performance, programmability & lower TCO

#### Enterprise use cases

#### High-end router, Firewall/security data plane

#### Data plane only

#### Switch, WLAN controller Line card/controller

#### **Benchmarks**

Compute performance

- SPECINT2006

- SPECINT2017

- CoreMark

Memory subsystem

- LMbench

- Stream

- TestPMD

- L3 Forwarding

- iPerf/Netperf

Application benchmark

- IPSec gateway

- kTLS

- Open offload

- SNORT/Hyperscan

- NVMEoF

- ML Inference

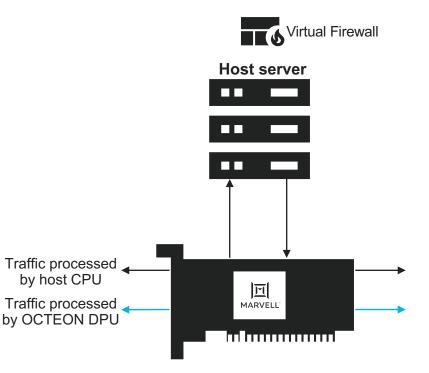

### 200Gbps open offload performance

- Full Firewall VM running on Host server

- Marvell DPU as fast path engine maintain route/firewall cache based on OpenOffload

| CN98xx 2Ghz, 2x100G |      |      |      |       |       |       |  |  |  |

|---------------------|------|------|------|-------|-------|-------|--|--|--|

| Data plane          | 64B  |      | 512B |       | 1518B |       |  |  |  |

| cores               | Mpps | Gbps | Mpps | Gbps  | Mpps  | Gbps  |  |  |  |

| 2                   | 3.54 | 2.38 | 3.54 | 15.1  | 3.46  | 42.5  |  |  |  |

| 10                  | 15.7 | 10.6 | 15.7 | 67.1  | 15.6  | 191.9 |  |  |  |

| 30                  | 43.1 | 28.9 | 43.1 | 183.5 | 16.2  | 200   |  |  |  |

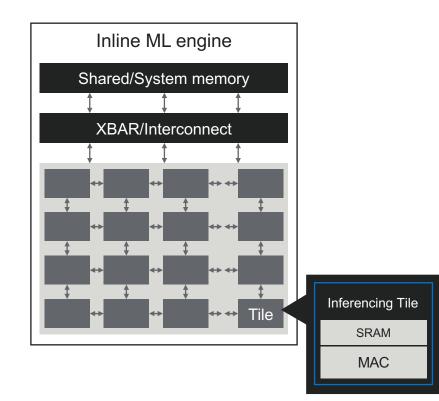

## Integrated ML engine

#### Best-in-class DPU inferencing

- Directly in the data pipeline

- Each ML tile contains private SRAM

- Ultra low power

- Up to 100x performance vs SW

- Supports Int8, FP16

- Accelerated Tanh and Sigmoid activation functions

- Use cases

- Threat detection

- Context-aware service delivery

- QoS

- Beamforming optimization

- Predictive maintenance

#### Summary

Software-defined infrastructure requires hardware acceleration – OCTEON<sup>®</sup> portfolio has right accelerators to deliver best solution TCO

Unified software stack built on open source frameworks and benchmarks demonstrate leadership across broad workloads

2

3

#### Thank You

Essential technology, done right<sup>™</sup>

#### **Session 5: Design**

#### Increasing Data-Center Reliability by Predicting Defects and Monitoring Aging

- Marc Hutner, Senior Director of Product Marketing, proteanTecs

- A New Way of Measuring Heterogeneous-SoC Performance

- Hanan Moller, Technical Director, Siemens

#### Advanced Semiconductor Manufacturing Technologies for Quantum Computing

Anthony Yu, Vice President, Silicon Photonics Product Management, GlobalFoundries

## Increasing Datacenter Reliability by Predicting Defects and Monitoring Aging

November 2022

Marc Hutner | Senior Director of Product Marketing www.proteanTecs.com

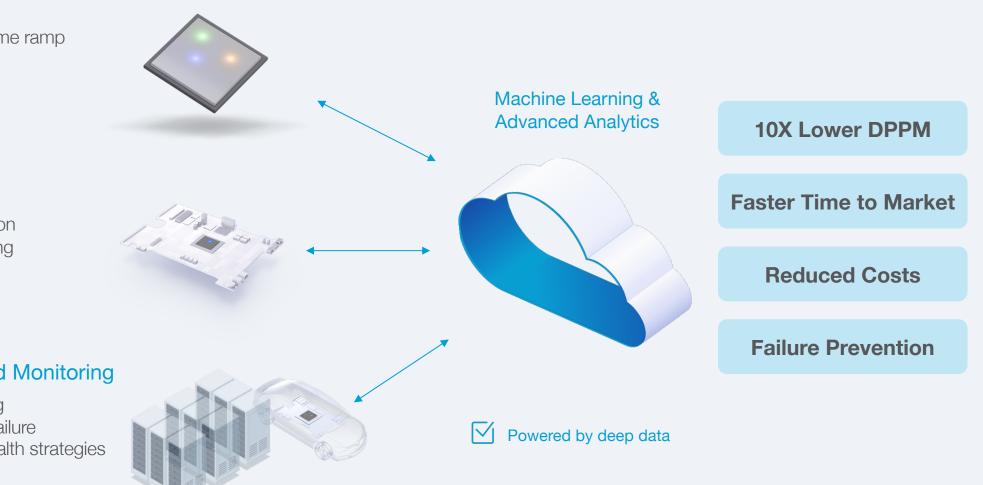

### proteanTecs at a Glance

Deep data health & performance monitoring for advanced electronics

Founded in 2017 by Addressing 50+ design industry leaders and industry-wide wins. In-use & co-founders of challenges of production-**Mellanox** scale proven **Sto** Customers in multiple key segments including **Datacenter**, Automotive,

**Communications, and Mobile**

New category with a multi-disciplinary approach

In use and production ready in advanced **FinFET nodes from leading Foundries**

#### **Global Footprint**

#### **Alliance Members:**

**Open Innovation Platform**<sup>®</sup>

**protean**Tecs 2

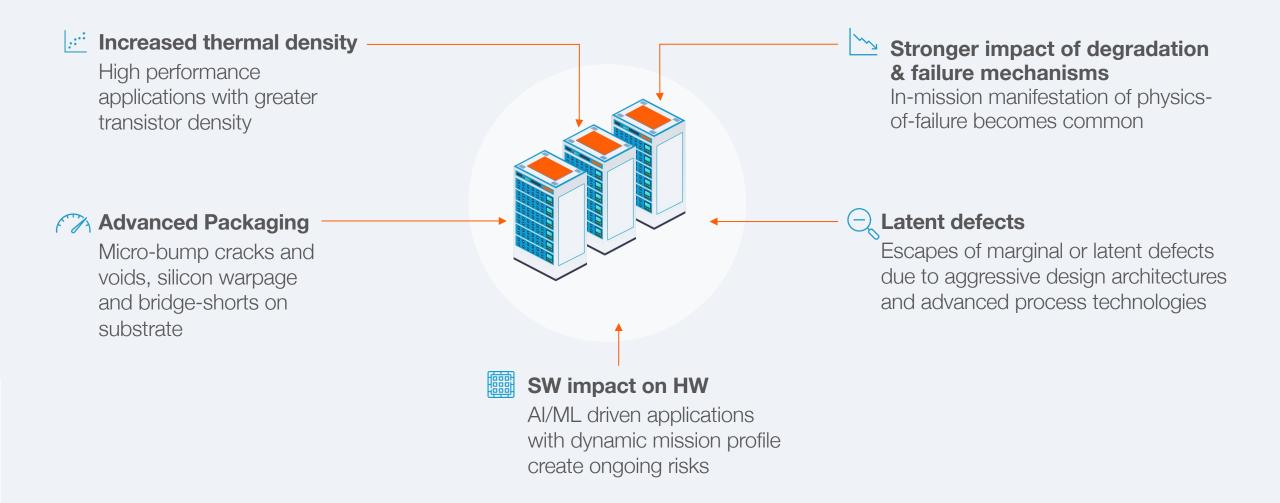

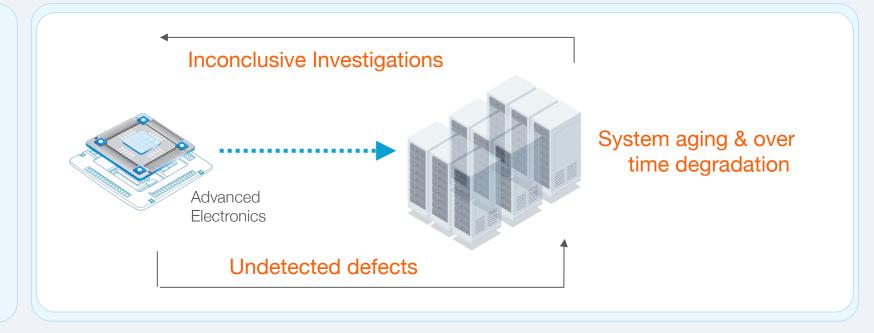

#### **Increasing Challenges in Advanced Electronics**

## **Real Examples of Datacenter Failures**

#### The New York Times

"Increasing complexity in processor design, smaller transistors, 3D chips and new designs that create errors only in certain cases all contributed to the problem"

"Several years ago, Google production teams began \to report errors that were maddeningly difficult to diagnose. Calculation errors would happen intermittently"

#### Market leaders are looking for answers from the industry

#### facebook.

"Silent data corruption due to silicon latent defects and aging. (1,000 DPPM!)" **Microsoft**

"Frequent unexplained HW failures with "No Issue Found" at high rates"

4.

"Rare, short-term computational errors on systems that passed all manufacturing tests successfully"

4 / proteanTecs

- "Silent Data Corruptions at Scale"; Harish Dattatraya Dixit Et. Al., Facebook, arxiv.org/abs/2102.11245, Feb. 2021

- "Cores that Don't Count"; Peter H. Hochschild Et. Al., Google Research, Jun. 2021

"Improving Cloud Scale Hardware Fault Diagnostics", Neeraj Ladkani, Rama Bhimanadhuni, Microsoft, Mar. 2020 OCP Virtual Summit The New York Times, "Tiny Chips, Big Headaches", February 16, 2022

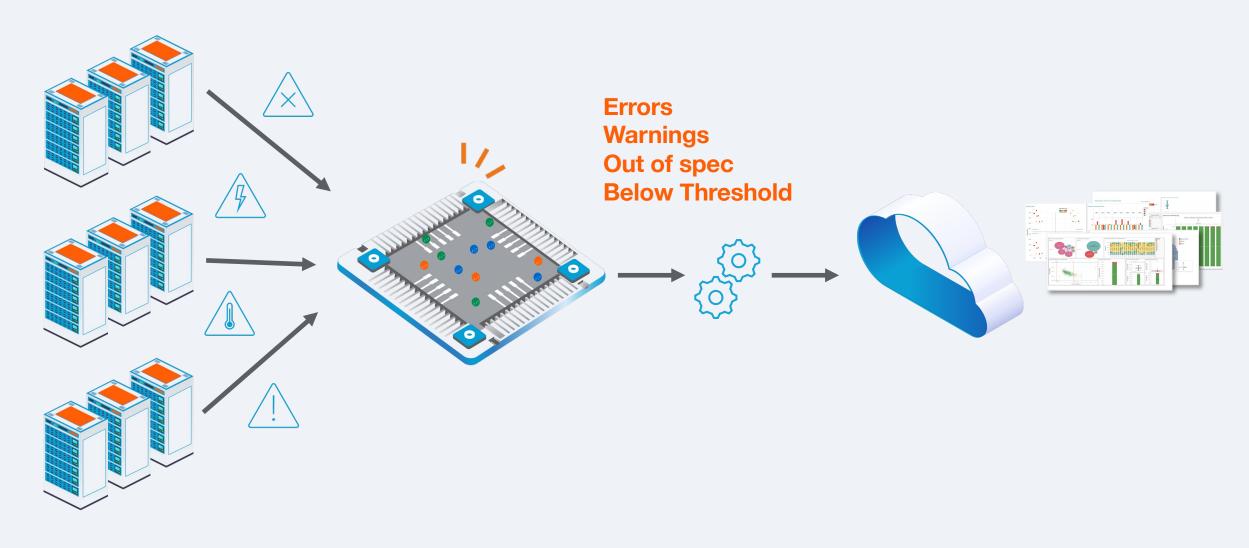

#### The Chip as a Smart Datacenter Monitor

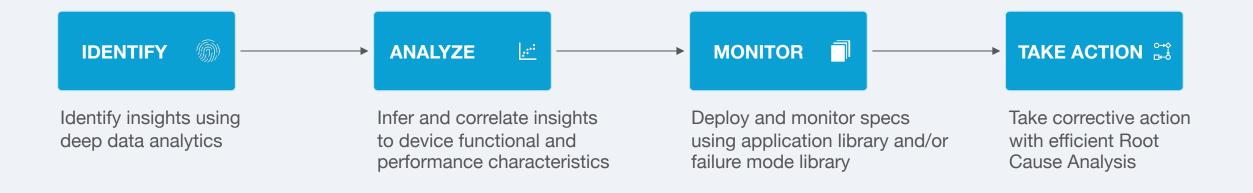

## **Driving Visibility and Actions at Every Stage**

#### **Chip Production**

- Higher confidence volume ramp

- DPPM reduction

- Performance yield

- Power reduction

#### System Production

- Performance optimization

- Environmental monitoring

- Quality monitoring

- SW<>HW optimization

#### Applications for In-Field Monitoring

- Performance monitoring

- Alerts on faults before failure

- Power/performance/health strategies

## Universal Chip Telemetry<sup>™</sup> (UCT)

## **On-chip Agents built for analytics**

- Parametric measurements

- High coverage & high resolution

- Minimal PPA impact

- Operate in mission-mode

- Sense the surrounding electronics

- Application optimization to HW

#### Automated Health Monitoring for Production

#### **Automated Health-Monitoring Production Workflow**

#### Use cases for Chip Production

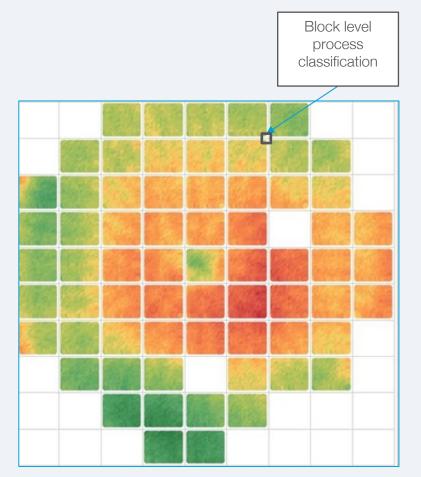

### **Personalized Device Assessment**

High granularity process parameter measurements (wafer, die, block)

## From a pass/fail per-chip view to a parametric per-block view

- 1. Post-to-pre silicon correlation

- 2. Inferred process parameters

- **3.** High resolution OCV

- 4. Vmin/ Fmax predictions

- 5. Smart material selection

- 6. Performance yield optimization

- 7. Bin planning

- 8. Advanced debug

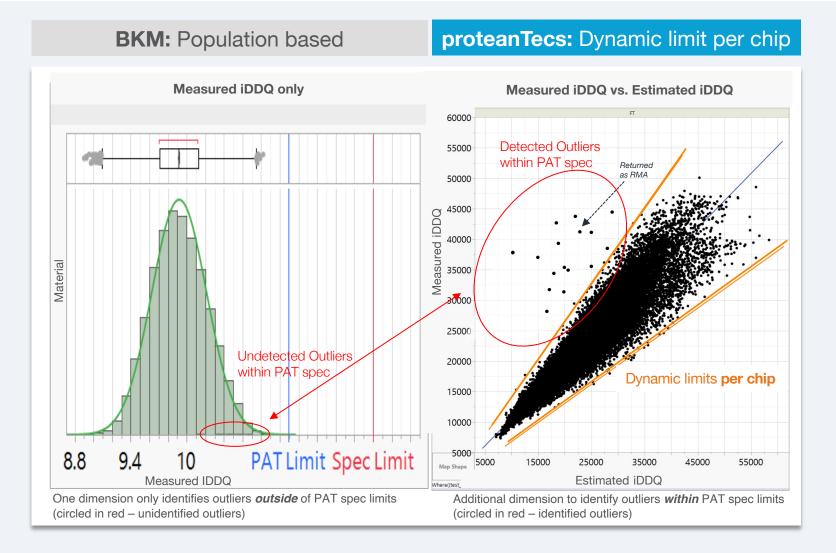

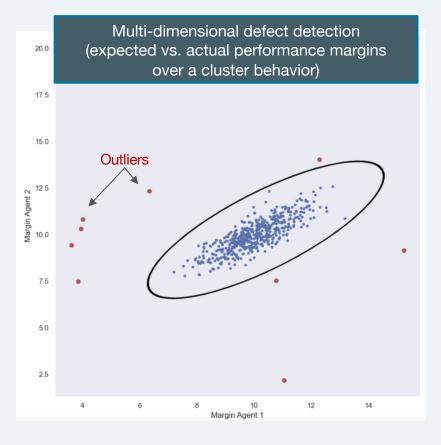

## **Prediction Based Per-Die Outlier Detection**

- Personalized chip assessment

- Multi dimensional outlier detection

- Yield reclamation

12 / proteanTecs

Fast RMA with pinpoint Root Cause Analysis

## **Margin Based Latent Defect Detection**

- Detection of extrinsic failures (latent defects) to prevent RMAs

- Margin quantification of the **path delay of millions of paths** (X% coverage) provides **parametric measurements**

- Sense and determine if the path delay is different than expected and mark the unit as **suspected/ marginal**

- Could be caused by defects in frontend processes (transistor defects) or backend processes (missing vias, small bridging defects)

Remaining margin: 9ps

Remaining margin: 18ps

Remaining margin: 36ps

#### Use cases for System Production

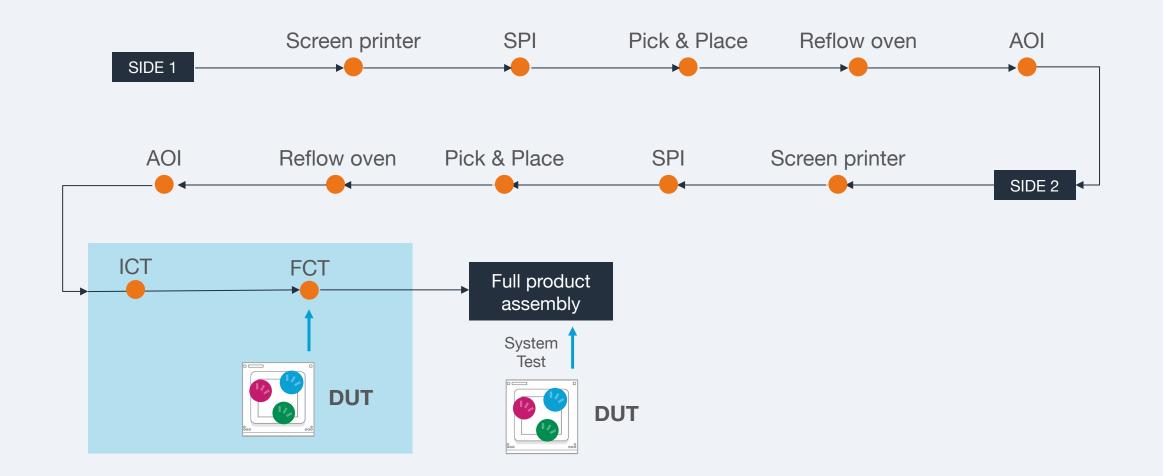

#### High Volume System Production Typical board assembly line

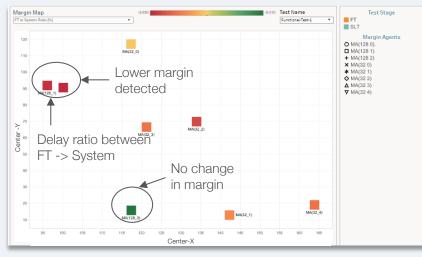

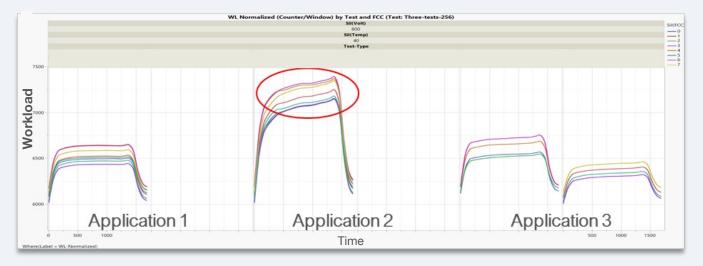

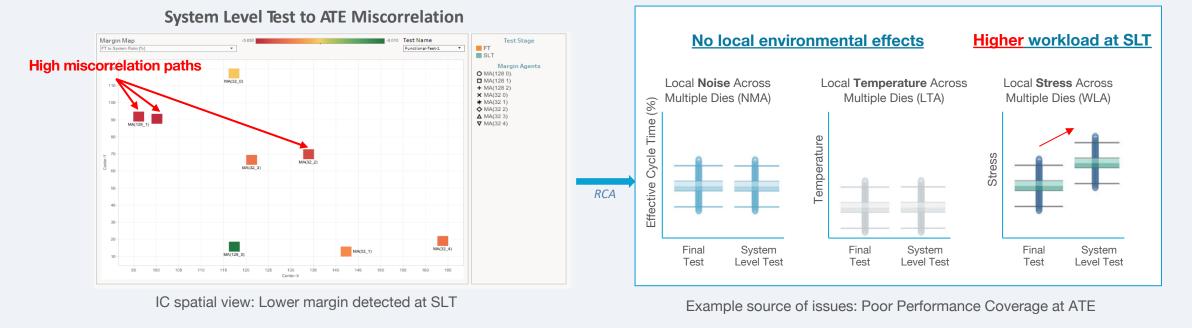

#### Fast Identification of Software Performance Issue

- Example: Lower margin detected at System Level: root caused to the effect of the application functional tests as measured by the system level, with correlation to workload and operational measurements

- Demonstrates the impact of different system level applications on the chip performance

IC spatial view of Margin measurements

Workload root cause analysis

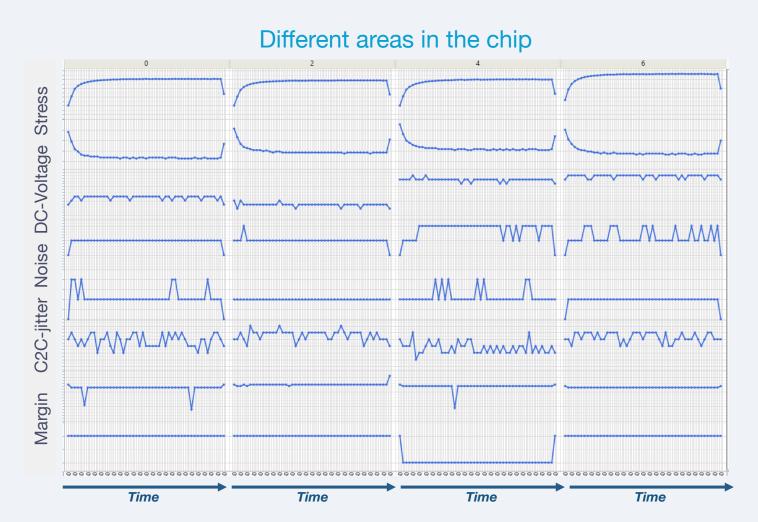

### **System Performance Monitoring**

Agent data recorded throughout multiple phases of system operation:

- Configure

- Operation Start 1

- Operation End 1

- Idle 1

- Idle 2

- Operation Start 2

- Operation End 2

- Idle 3

- Idle 4

- Correlating and merging different Agent measurements

- Margins of millions of paths

- IR drop

- Workload/stress: V\*T\*Toggle rate

- Cycle to cycle clock jitter

17 / proteanTecs

## Bring up & Production EOL software optimization and performance tuning

© proteanTecs 2022. All rights reserved.

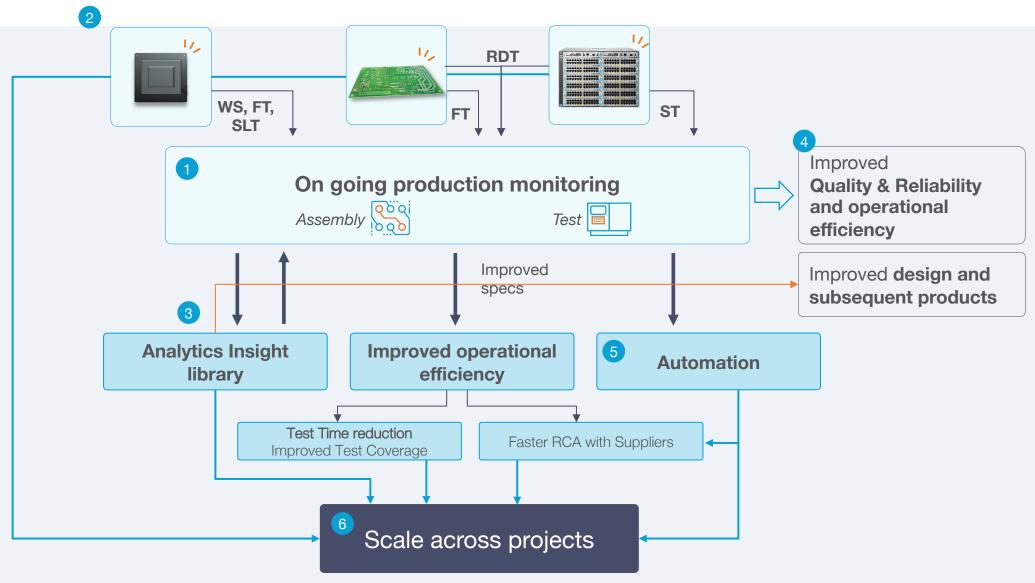

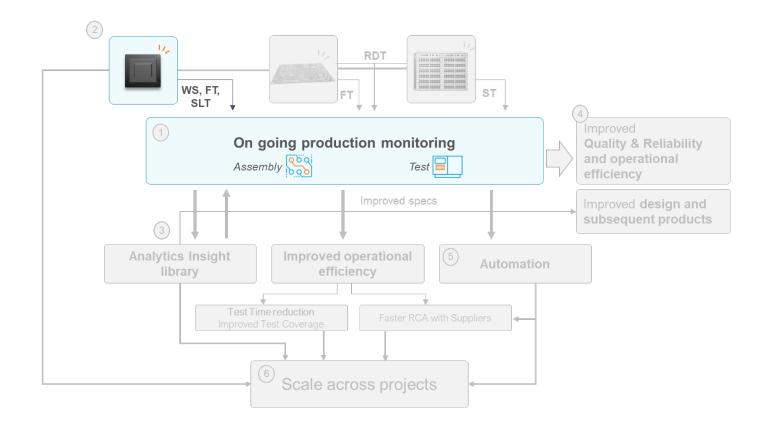

#### **Correlation Across Stages/ Setups/ Tests**

#### Accurate correlation & validation between stages: setup and test stress

Optimization of test conditions across all test stages (WS, FT, SLT, ST)

- Test limits and guard-bands, test equipment validation, etc.

- Accurate characterization of operational, environmental and stress effects

- ATPG structural test tuning correlative to real application at system

- Common data 'language' between ATE and system test

18 / proteanTecs

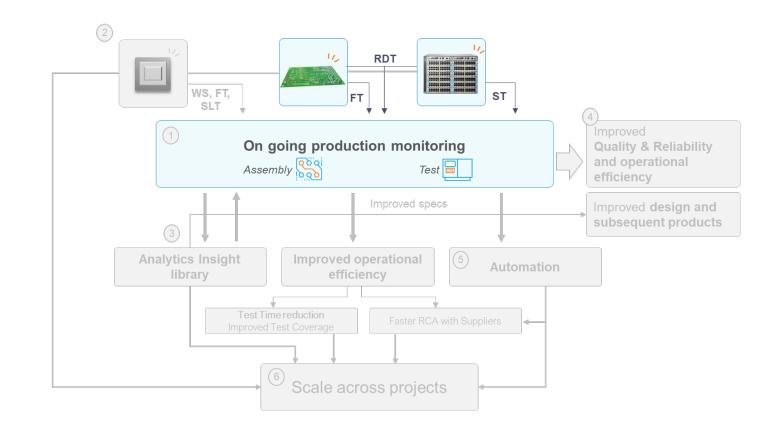

## **Automation at Test Production Line**

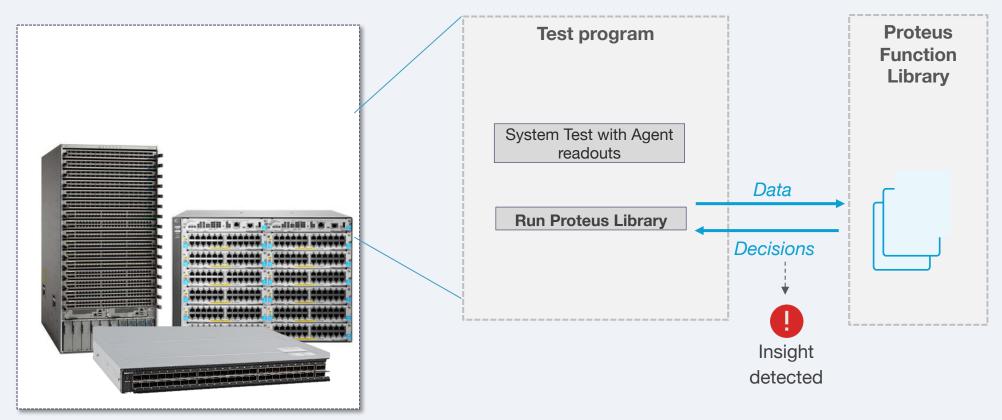

- Edge libraries are deployed to production line test for real time decisions

- Insight monitoring and operational efficiencies (test time reduction, skip-test)

#### Health-Monitoring Automated Workflow for Production

New methodology for predictive analytics with ML-driven on-chip telemetry

- Structured monitoring with continuous learning loop for existing product

- Scale for subsequent products with automatic deployment of libraries and improved specs

#### Use cases for In-Field Health and Performance Monitoring

#### **Continuous Performance Monitoring with On-Board Diagnostics**

Edge application: Lowering the operational risks

- Misbehaviour  $\rightarrow$  <u>close to failure</u>

- Manipulation → <u>out of reference</u>, security breach or tuning

- Misuse → <u>out of spec</u>, violation of operational requirements

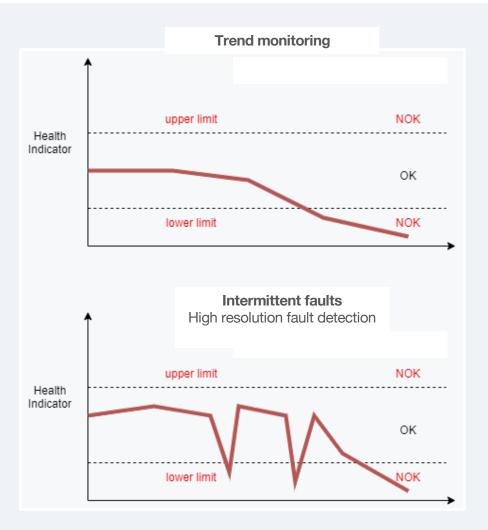

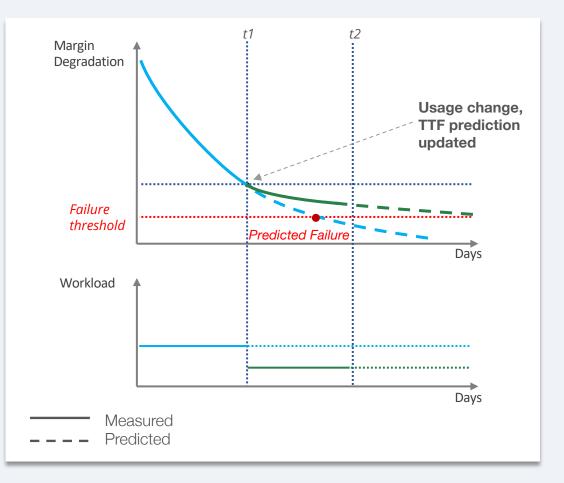

## **Performance Degradation Monitoring**

#### Based on Margin and Workload- Real operation

- Margin measurements covering real paths

- Using frequency degradation as a precursor of failure (both intrinsic and extrinsic reliability)

- Covers latent defects (extrinsic reliability issues)

- **TTF prediction** based on Margin Agents measurements

- Works with Workload measurement to track usage changes

#### **Continuous Performance Monitoring Edge application with built in diagnostics**

- Timing margin failure

- Microcontroller overstress failure

- Local voltage failure (AC)

- Local global voltage failure (AC)

- Power delivery network fault (DC)

- Power delivery network failure (AC low frequency)

- Effective local clock failure

- Clock source failure

- Thermal runaway

- Local thermal hotspot

- Connectivity failure

In-Field

## **Optimize, Monitor and Scale**

# Reuse libraries for other Chip and System projects SCAL

## Thank you.

marc.hutner@proteanTecs.com

## A New Way of Measuring Heterogeneous SoC Performance

Hanan Moller– Technical Director

**Tessent Embedded Analytics - Siemens**

Hanan.Moller@siemens.com

Linley Fall Processor Conference November 1 - 2, 2022

# Agenda

Introduce a performance measurement methodology that combines debug and monitoring IP

#### Hardware, software and use cases all contributing to complexity

Workloads defined by diverse businesses...

are executed in diverse usage environments...

...using new generations of semiconductor systems

| Cloud/<br>datacenter | Enterprise           | Service<br>provider | CPU<br>subsystems   | Accelerators               | Wired<br>interconnect |

|----------------------|----------------------|---------------------|---------------------|----------------------------|-----------------------|

| SMB/<br>SOHO         | Medical & industrial | Automotive          | Interconr<br>Memory | ect (NoC, inte<br>Security | wireless              |

Need to measure pre- and post-silicon performance and provide feedback from the field into both dev ops and design for the next generation

## Complexity, increasing software workloads and continuous improvement require a new approach

Validation now an essential step in design implementation Pre- and post-silicon Requires "whole system" view including the real software workload

Existing tools and techniques are inadequate Not built for today's levels of complexity Not built for automated testing processes

Feedback of behavioral data is essential Move from waterfall to continuous improvement Ideally need to retain visibility even after deployment

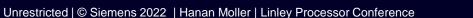

#### Traditional emulation, prototype and simulation flow

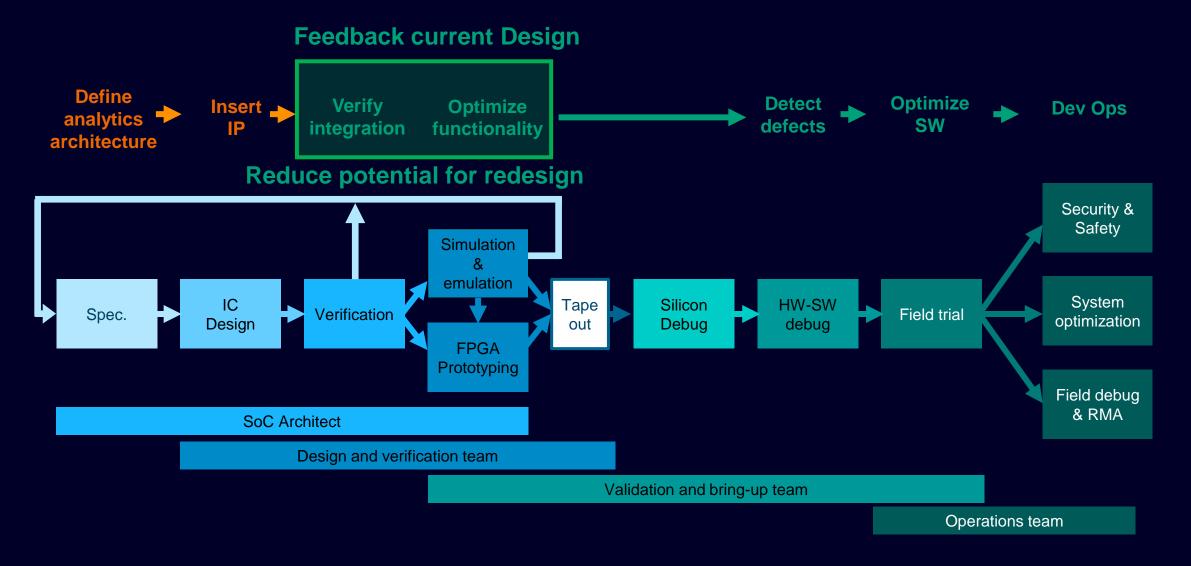

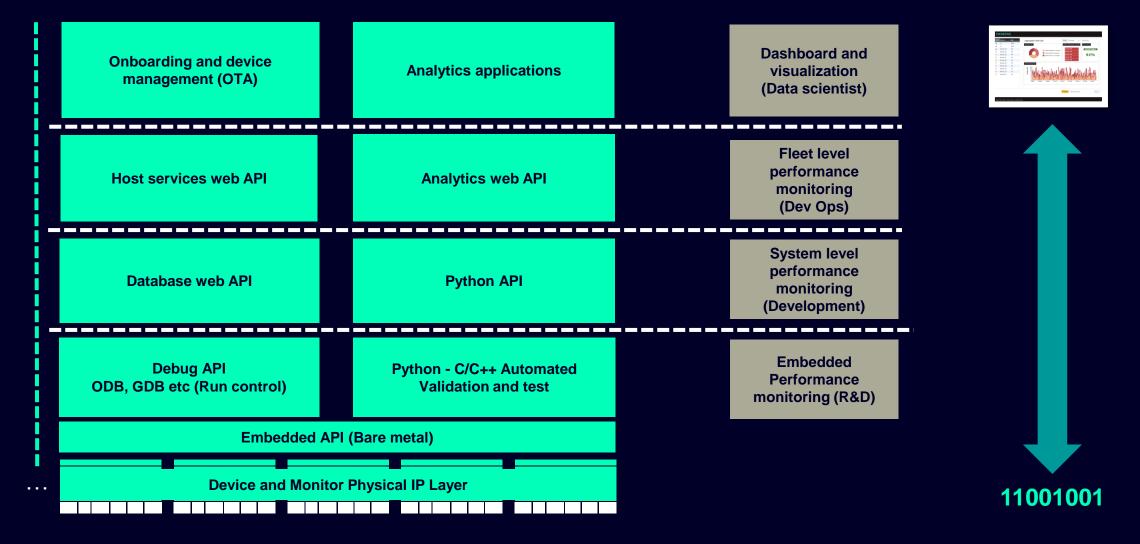

## Adding post-silicon visibility in your development flow

## Consider validation and performance requirements beyond the device

Chip developer Integrates Embedded Analytics into ICs EA-enabled devices

### **Benefits**

- Faster product sign-off

- Fewer bugs

- Effective use of HW

resources

### **Embedded system manufacturer**

Builds and monitors products using EA-enabled devices

**EA-enabled product fleet**

### **Benefits**

- Optimized apps under real workloads

- Monitor safety / secure transactions

- Better remote debug and long tail bug analysis

### **System operator**

Operates products with devices from many manufacturers EA-enabled facilities

### Benefits

Insights into CAPEX, OPEX, SLAs and security

SIEMENS

RMA

## Common requirements for an automated post-silicon validation solution

Software / firmware teams need hardware designs and software infrastructure that support the move to automated, scalable validation and root cause analysis

- Concurrent software debug and silicon validation capturing HW/SW interactions

- The right data must be observable and available for on-chip and off-chip analysis

- The ability to inject, detect or correct faults, errors and other stimulus

- Must be able to locally deal with unexpected or non-deterministic behaviors

- Remote access to targeted insights and actions, not petabytes of raw data

- Instrumentation costs must be kept to a minimum (PPA, BW, servicing etc)

#### Unrestricted | © Siemens 2022 | Hanan Moller | Linley Processor Conference

### SIEMENS

# Example case study with post-silicon validation

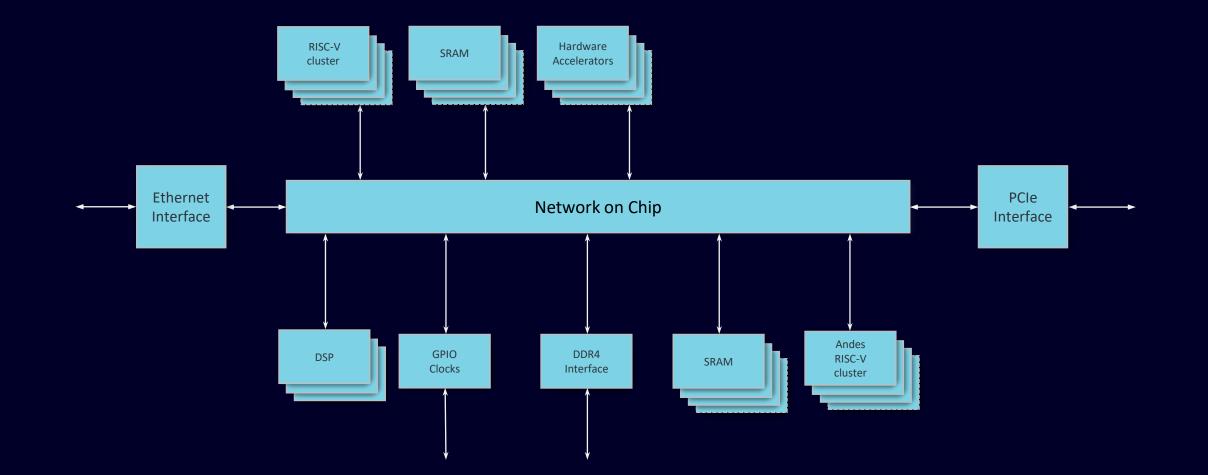

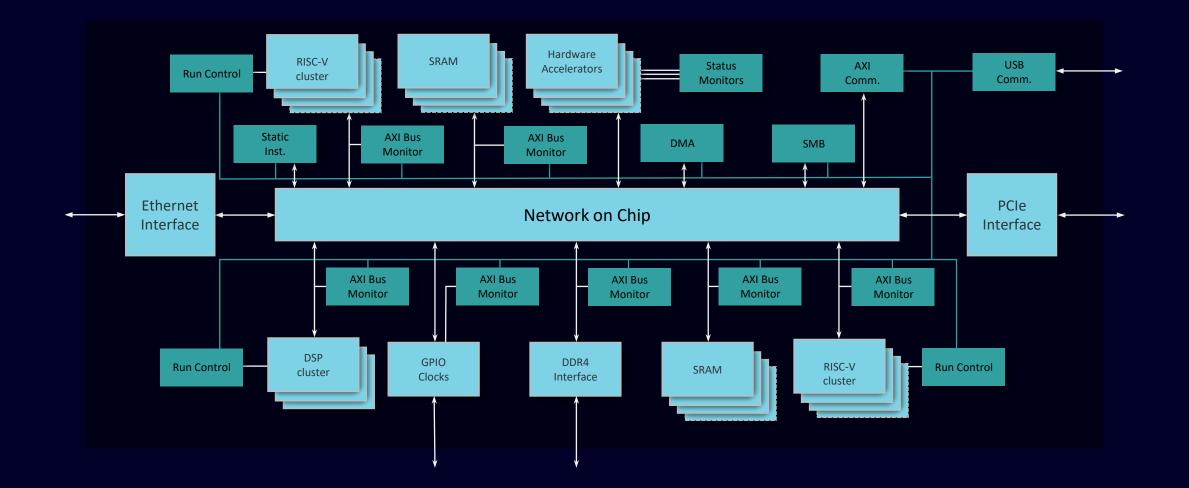

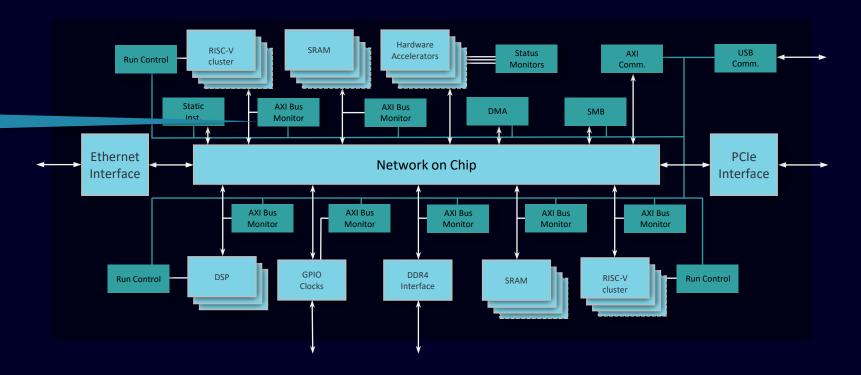

## **Example heterogeneous SoC architecture**

## SoC instrumented with validation IP

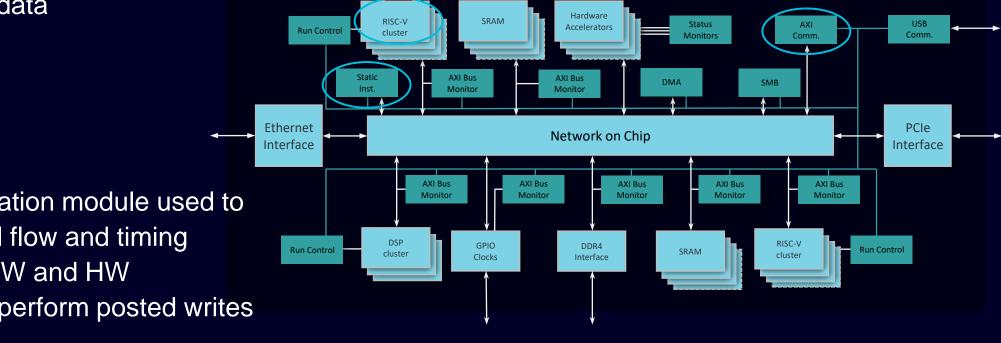

## **NOC** deadlock detection, out of range - forensic trace

Bus Monitor – Continuously trace all traffic

Conditional trace triggered if transaction duration exceeds threshold (eg 5k cycles, value or address range)

Signal invalid operation and save trace for analysis

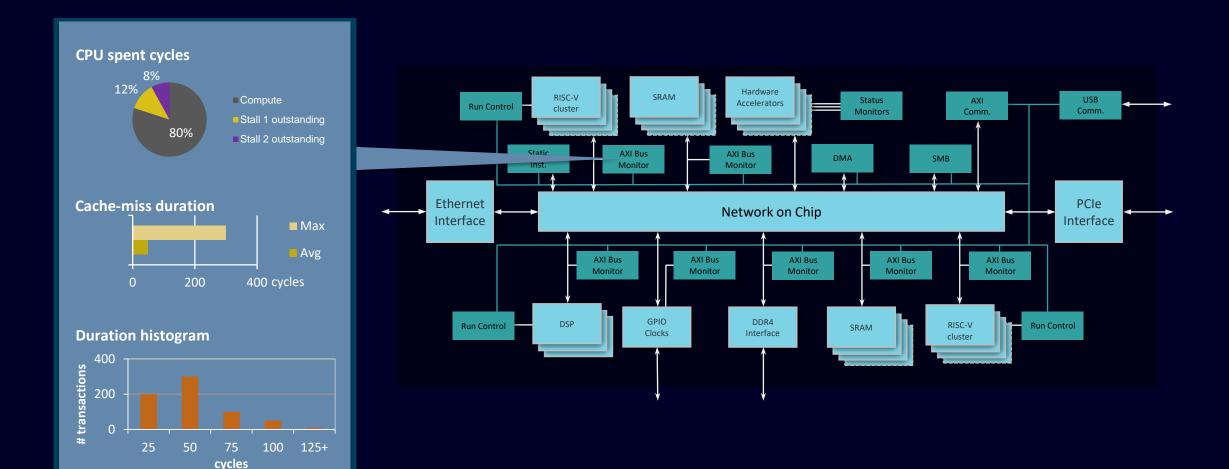

## **Application thread timing and CPU performance loss**

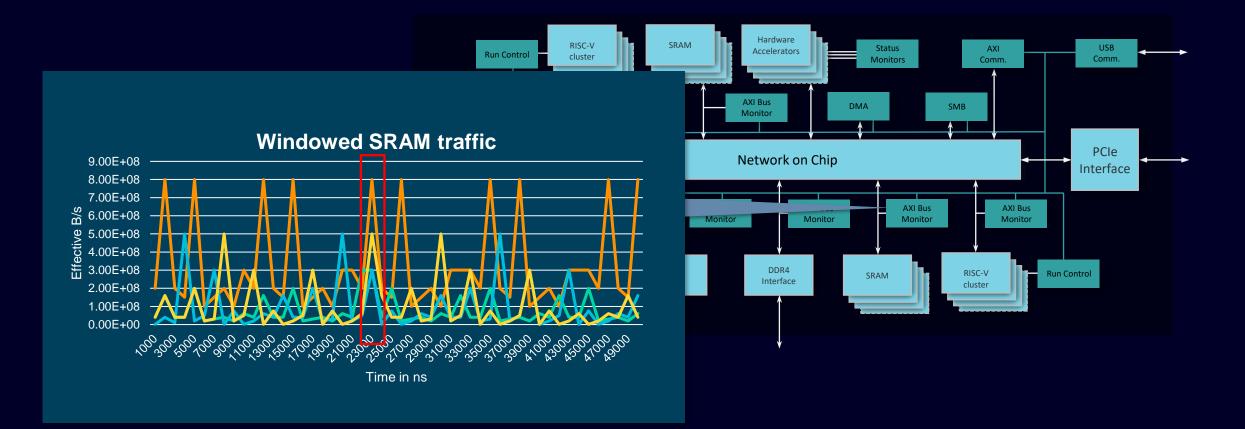

## Memory bandwidth and access performance

## Implementing runtime analytics and reporting on-chip

Use a main system CPU or dedicated processor to configure the monitors and analyze data

### Analytics CPU configures monitors and collects data via the AXI Communicator

Static Instrumentation module used to determine control flow and timing Application SW and HW accelerators perform posted writes to here

## A complete technology stack is required for silicon and system lifecycle management – turning 1's and 0's into insight and performance metrics

## **Conclusions and call(s) to action**

- New pressures and working methods mean that traditional debug and validation techniques sometimes aren't enough

- Increasing complexity | changing workloads | continuous improvement

- Silicon architects and hardware designers: think about system and software validation up-front

- Technology exists to dramatically improve these processes with minimal PPA penalty

- Software teams: software-based tools aren't everything... the HW team can probably help

- Support from the hardware team will make your life much easier and efficient

- Tessent Embedded Analytics provides unprecedented system-level visibility

- Integrates into automated workflows

- Automates configuration and data collection

- Helps identify issues and root-cause them fast including hard-to-replicate bugs

# Contact

Published by Siemens DI SW

Hannan Moller Technical Director, Solution architecture, Embedded Analytics Tessent Silicon Lifecycle Solutions

E-mail Hanan.Moller@siemens.com

## Advanced Semiconductor Manufacturing Technologies for Quantum Computing

## Anthony Yu

Vice President, Product Management GlobalFoundries

anthony.yu@gf.com Linley Fall Processor Conference, November 1-2, 2022

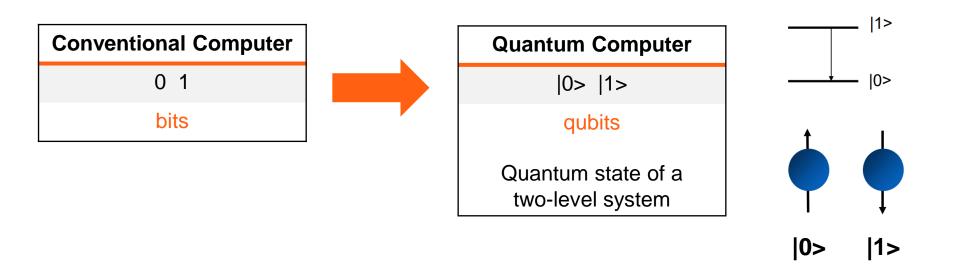

# Foundry support for creating quantum computers

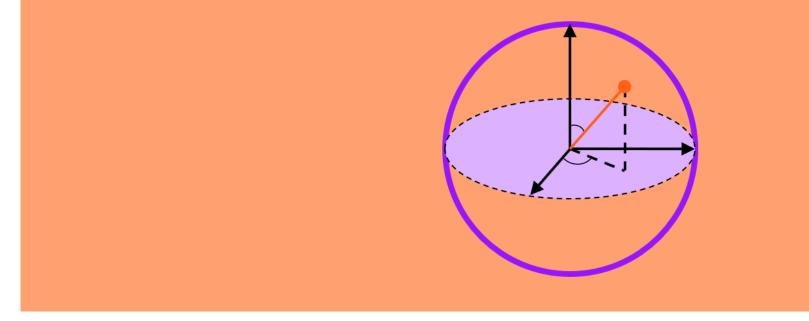

Moving from *bits* to *qubits*

Requires a long term vision to create critical building blocks, whether the approach is matter-based (e.g. quantum dots) or photonics-based

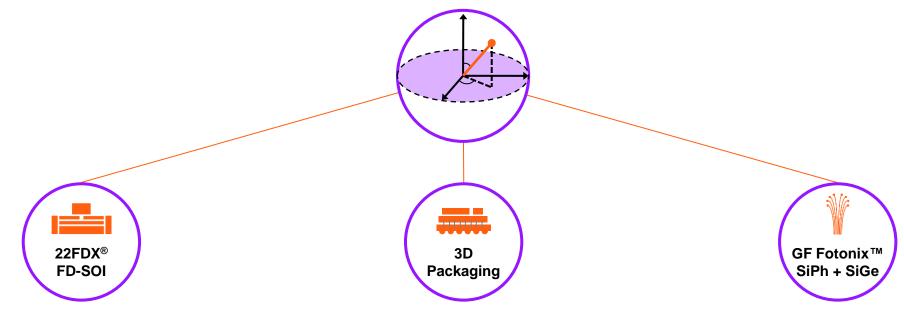

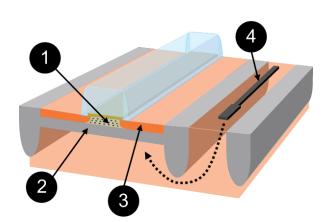

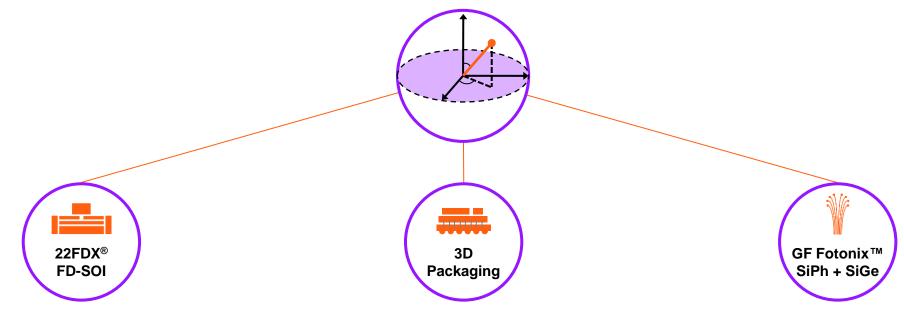

## **GF** platforms enable quantum systems

- Fully Depleted SOI

- 22nm monolithic integration for IoT / ATV, elite wireless perf

- ULL, sub THz, back gate IP

- Cyrogenic low temp design

- Spin Qubit CNOT QD confinement and control in UT SOI

- 3D system integration

- 12nm/22nm logic and analog with 3D interconnect

- 1.44um 3D pitch W2W/D2W

- Si, FDX, SiPh

- TSV and µBump

- Co-packaged thermal and stress solutions

- Monolithic SiPh

- 45nm electronics and photonics in a single chip

- 300GHz ft/fmax, photonic waveguides VIS to Cband

- Integration: laser, fiber, MEMs

- HP SiGe companion tech for LNA, TIA

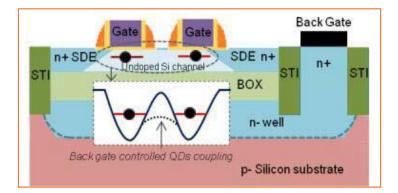

## 22FDX<sup>®</sup> platform offers unique capabilities for QD storage & control

GF's 22nm Fully-Depleted Silicon-on-Insulator technology – Optimal combination of digital and mmWave

22nm FD-SOI transistor architecture uniquely benefits cryogenic operation

- Ultra-thin 6nm silicon film allows for small transistor feature size in planar CMOS

→ Provides both transistor speed and spatial confinement

- 2. Thin 20nm buried oxide layer allows the transistor channel to be undoped

- $\rightarrow$  Avoids degradation from carrier freeze-out

- 3. Transistor body is electrically isolated from the channel, but electro-statically influences the channel

→ Body bias as an extra design knob to achieve operating point at cryo temperatures

- 4. Transistor drain on buried oxide minimizes parasitic capacitance

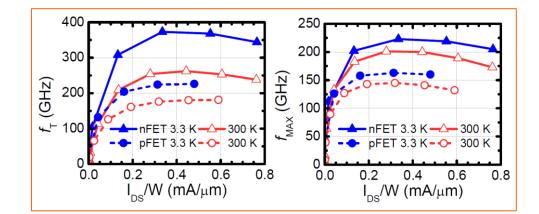

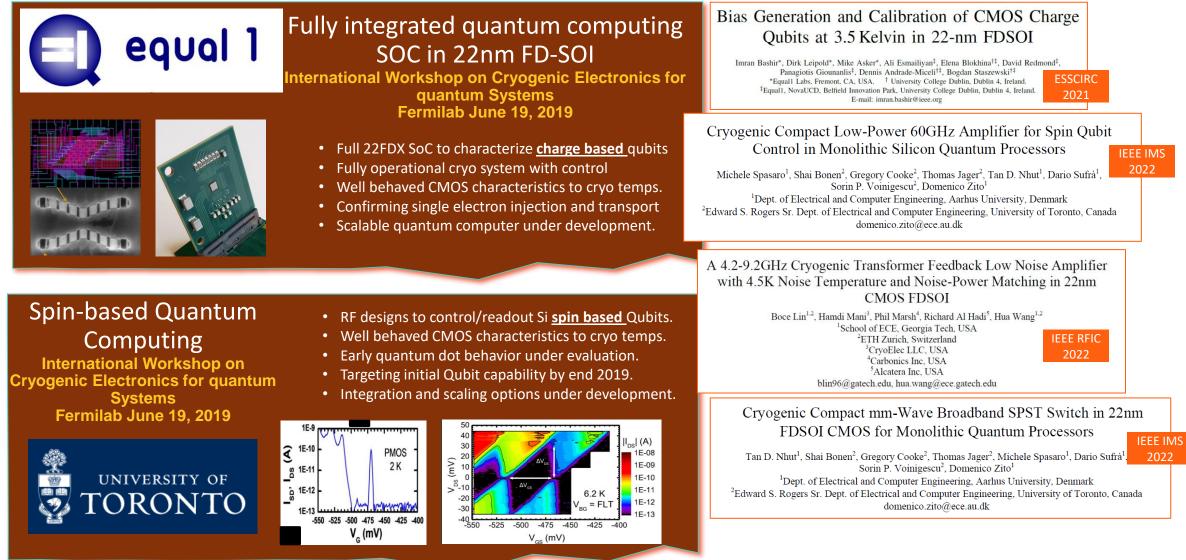

## **22FDX<sup>®</sup> platform for cryo temperature quantum computing**

- Key characteristics, such as fT/fMax, improve at cryogenic temperature in 22FDX technology

- Advanced-node minimum feature size helps create higher confinement for quantum dots

- Demonstrated possibility of monolithic quantum processor

- TIA gain measurement of 80dBΩ at 2K, better than at room temperature

- Back-gate bias eases design effort to maintain sweet-spot operating condition at 2K

Anthony Yu, November 1, 2022

## **Proof points of 22FDX® platform for quantum computing**

Anthony Yu, November 1, 2022

## **GF** platforms enable quantum systems

- Fully Depleted SOI

- 22nm monolithic integration for IoT / ATV, elite wireless perf

- ULL, sub THz, back gate IP

- Cyrogenic low temp design

- Spin Qubit CNOT QD confinement and control in UT SOI

- 3D system integration

- 12nm/22nm logic and analog with 3D interconnect

- 1.44um 3D pitch W2W/D2W

- Si, FDX, SiPh

- TSV and uBump

- Co-packaged thermal and stress solutions

- Monolithic SiPh

- 45nm electronics and photonics in a single chip

- 300GHz ft/fmax, photonic waveguides VIS to Cband

- Integration: laser, fiber, MEMs

- HP SiGe companion tech for LNA, TIA

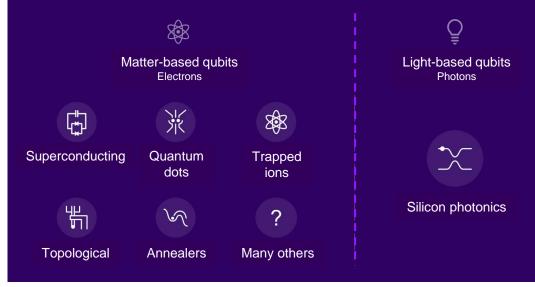

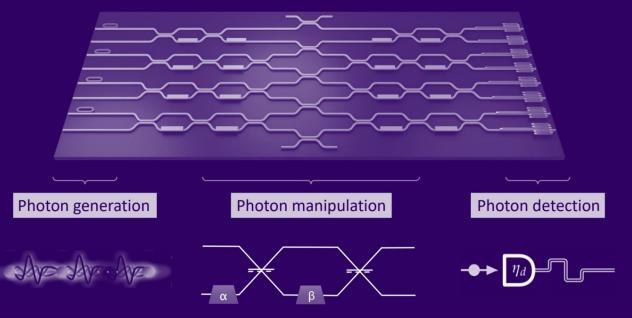

## Many ways to make a qubit

- Qubits can be any two-level system

- Spin of an electron

- Polarization of a photon

- Spin of a quantum dot

- Success of a quantum system depends on:

- Making

- Manipulation

- Entangling

- Need to remain in quantum states of superposition and entanglement (coherence)

- Coherence times long enough to allow for computation and for error correction

Source: PsiQuantum

## **Advantages of photons as qubits**

- Light (photons)

- Carries quantum information

- Works across all temperatures

- No crosstalk

- Can be manipulated using optical components built in a CMOS line

- Silicon Photonics is manufacturable

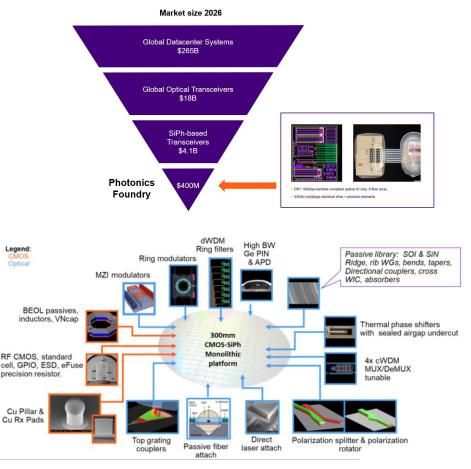

## DC optical interconnects underpin growth of photonics foundry market

### **GF** Fotonix<sup>™</sup> monolithic integration

Anthony Yu, November 1, 2022

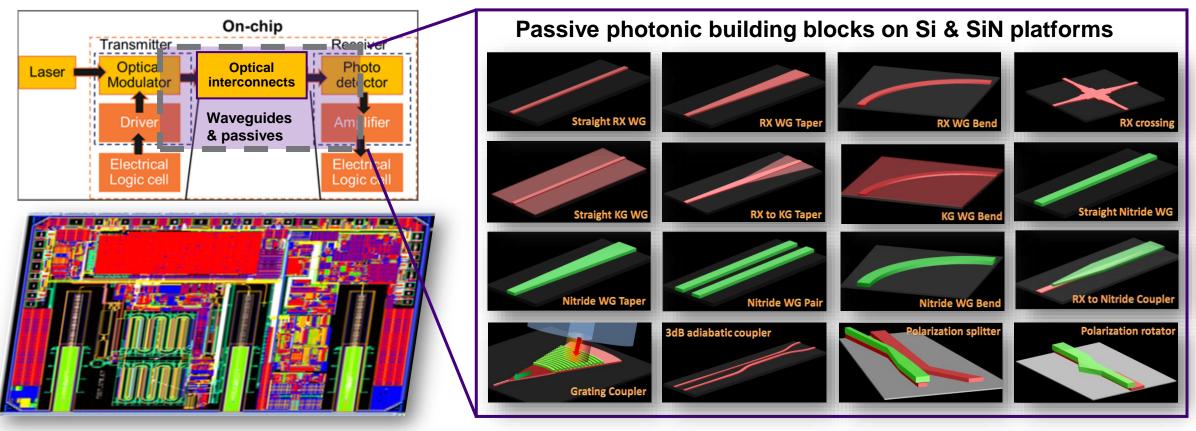

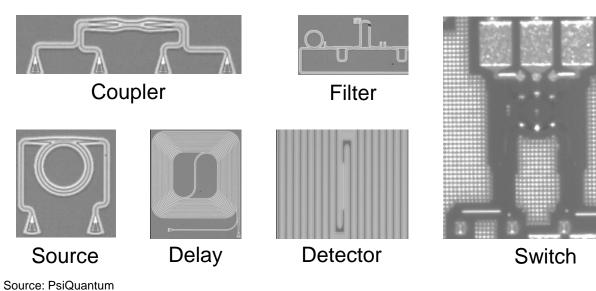

## **GF Fotonix<sup>™</sup> passive library**

Routing, coupling, polarization handling, wavelength filtering, etc.

#### Reference

K. Giewont, et al., IEEE JSTQE, 25(5) 1-11 (2019).

M. Rakowski, et al., OFC, T3H.3 (2020).

Y. Bian, et al., OSA FiO, FW5D.2 (2020).

- Si and SiN-based components covering both O and C-bands

- SOI SMF (-1.03dB/cm), SOI Rib (0.73dB/cm)I SiN (0.3dB/cm)

## **Building blocks**

The basic building blocks

Source: PsiQuantum

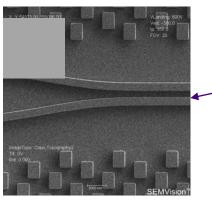

## **Manufacturing for quantum computing**

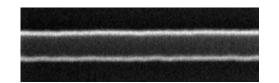

Loss is the enemy: True in all optics, paramount in quantum computing

### Datacom/Telecom

- Waveguide loss = <1 dB/cm

- Supports link budgets for traditional pluggable transceivers or next generation co-packaged optics

- Silicon waveguides accomplish this in GF Fotonix<sup>™</sup>

- Utilizes advanced immersion lithography for reduced Line Edge Roughness (LER)

- ~2X improvement in loss over non-immersion

|                    | Dry Lithography  |     | Immersion Lithography |     |

|--------------------|------------------|-----|-----------------------|-----|

| Features           | CD Sigma<br>(nm) | LER | CD Sigma<br>(nm)      | LER |

| 150nm<br>Waveguide | 0.99             | 6.4 | 0.32                  | 3.5 |

| 350nm<br>Waveguide | 0.87             | 6.8 | 0.40                  | 3.8 |

| 400nm<br>Waveguide | 0.94             | 6.1 | 0.31                  | 3.3 |

### Photonic Quantum Computing

- Waveguide loss = <<1 dB/cm

- Necessary to support single photon fidelity from generation to detection

- Utilizes same advanced immersion lithography

- Incorporates SiN for key low loss waveguide structures

- Common material, already used in GF FotonixTM

- Optimizing the deposition process for extremely low loss performance

SiN waveguides will support very low loss waveguides (top view)

Anthony Yu, November 1, 2022

## **Manufacturing for quantum computing**

### Same base process, new material integration

- Photonic-based quantum computing leverages the advantages of GF Fotonix<sup>™</sup> silicon photonics platform

- Advanced tooling Industry-leading manufacturing

- Rigorous process controls Manufacturability and reliability

- The full life cycle of the photon is supported in silicon

- Photon creation through detection

- This makes scaling to a 1,000,000 qubit machine possible

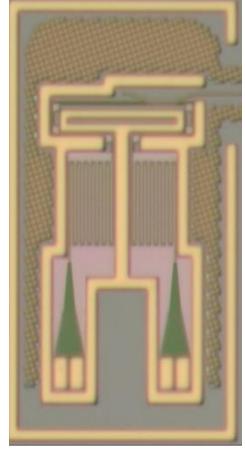

- Quantum computing has specific component needs

- High speed optical switches Significantly better loss than Si-based switches

- Efficient, low loss manipulation of single photons

- Single photon detectors Superconducting detection

- Key basis of qubit creation to drive compute architecture

- These are being integrated and using our standard process and toolset

Single photon detector

## Manufacturable components built for quantum computing

### Manufacturable components

### Waveguide propagation loss

### Single mode Si waveguide

Anthony Yu, November 1, 2022

GlobalFoundries © 2022 All Rights Reserved

# Foundry support for creating quantum computers

- Foundry platform technologies address certain portions of the quantum computing solution

- Examples: 22FDX<sup>®</sup>, 3D integration, Silicon Photonics

- Using photons as qubits leverages high volume CMOS foundry

- Mirrors, beam splitters and phase shifters move photons along circuits in chips networked by fiber. Results are read using photon detectors.

- Known silicon technology makes photonic qubits inherently scalable

- New exotic materials must be carefully considered for predictable performance

Source: PsiQuantum

## **GlobalFoundries**<sup>™</sup>

# Thank You

The information contained herein is confidential and the property of GlobalFoundries and/or its licensors.

This document is for informational purposes only, is current only as of the date of publication and is subject to change by GlobalFoundries at any time without notice.

GlobalFoundries, the GlobalFoundries logo and combinations thereof are trademarks of GlobalFoundries Inc. in the United States and/or other jurisdictions. Other product or service names are for identification only and may be trademarks or service marks of their respective owners.

© GlobalFoundries Inc. 2022. Unless otherwise indicated, all rights reserved. Do not copy or redistribute except as expressly permitted by GlobalFoundries.

techinsights.com

## Thank You!